基于DM6446的视频编码器的硬件设计

2025-03-07

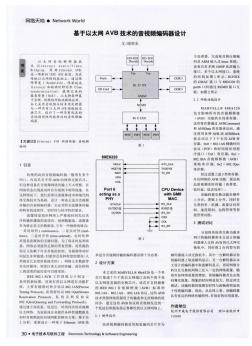

设计了一套基于TMS320DM6446的视频压缩系统。主芯片采用TI公司的TMS320DM6446,模拟视频信号送入解码器TVP5150后,解码为符合ITU-R BT.656标准的数字视频信号,BT.656数字视频信号被送往TMS320DM6446,TMS320DM6446内嵌DSP实现视频信号的H.264压缩,内嵌ARM对压缩后数据进行打包并进行网络传输。实践证明,该编码方案很好地完成了数据压缩及传输,当码率为372 kb/s时,PSNR为39.18 dB(使用NEWS序列),符合设计要求。

为了解决标准清晰度监控系统中存在的一些问题,设计了一个基于tms320dm365的高清视频压缩系统。采用itu-t的h.264(dm365内嵌硬件压缩器)视频压缩算法,高清模拟视频信号通过专用视频解码芯片tvp7002转换成数字视频信号,在dm365中进行数据压缩,内嵌arm把数据打包后传到internet,通过pc机软件解码,进行视频播放。实践证明,本编码方案很好的完成了数据压缩及传输,符合设计要求。

86基于DM6446的数字视频通信系统的研究

编辑推荐下载

h.264/avc是itu-t和iso/iec两大国际组织共同制定的新一代视频压缩编码标准。指数哥伦布编码是熵编码的重要主要组成模块,对从码流中提取的句法元素进行编码。它与基于上下文自适应的可变长编码(cavlc)或基于上下文自适应的算术编码(cabac)共同构成了熵编码。本文全面介绍了指数哥伦布的基本原理及本设计中指数哥伦布编码的句法元素,重点阐述了指数哥伦布编码器的硬件实现方法。实验结果表明,该设计能满足分辨率为1920×1080的视频序列的实时编码对质量和速度的要求。

简要介绍了tms320dm6446芯片,并采用该芯片设计了一款视频会议终端。该系统在满足视频会议实时性要求的情况同时,可获得更高的图像质量。

热门文档 基于DM6446的视频编码器的硬件设计

本文结合c64系列dsp芯片的特点,讨论基于tms320dm642dsp的mpeg-4视频实时编码算法实现和优化方法。优化通过修改适于dsp的数据结构,有效地分配片上核心内存,合理应用edma、缓存cache、线性汇编、软件流水、ccs优化工具等多种方法综合来完成。实验结果证明,这些方法提高了程序的并行性和存储器的访问效率,优化过的编码器可以实现实时编码。

设计了一种用fpga实现mpeg-4编码器方案。为进一步提高编码的效率,在算法和结构方面进行了优化。提出了带有判全零系数的loeffler快速dct算法,并采用"十字"形运动估计算法,设计了高度并行、紧凑流水线的fpga实现方案。用veriloghdl硬件描述语言编写了代码,在quartusii集成开发环境下,进行了fpga(field-programmablegatearray)系统仿真验证。测试结果表明,该设计编码高效,符合实时视频通信的需求。可广泛应用于移动视频通信和远程无线监控等领域。

在ti最新的davinci处理器tms320dm6467开发平台上实现了h.264视频编码的移植。重点阐述了davinci平台的特点及开发方法,分析了h.264的移植过程中遇到的难点,解决了该芯片内部dsp端和arm端之间的双核通信及h.264视频编码程序在双核系统中分割等问题。

在tms320dm642dsp平台上设计实现了mpeg-4视频编码器,并从算法改进、c代码优化、汇编代码优化等几个层次对编码器进行优化,以减小程序代码的复杂度和运算量,改善软件并行性.实验结果表明,优化后的编码速度提高了10倍以上,该编码器可以实时编码cif格式的视频序列.

以ti公司生产的基于达芬奇技术的最先进的媒体处理器tms320dm6467作为核心处理器。该设计根据tms320dm6467内部的视频编解码模块、以太网模块与vpif视频接口,采用多路视频解码器tvp5158与千兆以太网收发器et1011c,建立了移动视频服务器的输入与输出系统,实现了对移动视频的采集与发送。

精华文档 基于DM6446的视频编码器的硬件设计

详细阐述了针对adsp-bf561双核dsp芯片的h.264视频编码算法进行优化的具体方法。试验数据表明,优化后的编码器性能得到了全面提升,可以实现基于adsp-bf561双核平台上的4cif视频实时编码。

视频编码器的对比和选择 本文来自hulu全球高级研发经理、视频编解码与传输领域资深专家傅德良在 livevideostackcon2018热身分享,并由livevideostack整理而成。在分享中,傅德良以 hulu实践为基础,介绍了视频编解码标准与视频编码器间的纷争以及视频编码器对比中的 常见误区。 大家好,我是傅德良,在hulu主要负责的团队是在做音视频编解码和传输相关的一些优 化和开发的工作,很高兴跟大家聊一聊对于视频编码器的对比和选择。 主要内容分为以下三个方面: 1,纷争的视频标准与视频编码器 2,视频编码器对比中的常见误区 3,选择最合适的视频编码器 由于今天的热身分享时间相对比较有限,所以今天主要会讲常见误区这一块,关于选择最 合适的视频编解码器这个领域,更多的会在10月份的livevideostackcon2018正式分享 中进行介绍。 前言

介绍了在tms320dm6446dsp平台上实现avs视频编码器的算法设计与优化方法。在软件整体设计优化的基础上,重点对运动估计等算法进行了优化改进;同时针对平台特点给出结构优化方法,主要包括提高代码并行性及存储器和数据搬移的优化。测试结果表明,通过优化,在保证图像质量损失较小的情况下,编码器的编码速率有显著提高。

基于高速定点dsp处理器tms320dm642,设计并实现了一款嵌入式实时h.264视频编码器,提出了局部自适应预测运动估计算法.采用c64xcpu的软件优化技术,解决了视频编码的实时性问题.实验结果表明,h.264编码器对分辨率为320×288yuv格式视频信号的编码速率达到每秒13帧以上,且具有极低的码流速率和较高的图像编码质量.

文中详细阐述了针对adsp-bf561双核dsp芯片的mpeg-4视频编码算法的优化方法。实验数据表明,优化后的编码器性能得到了全面提升,实现了基于adsp-bf561双核平台上的4cif视频实时编码。

最新文档 基于DM6446的视频编码器的硬件设计

针对多媒体传输过程中需要对视频数据进行压缩、编码和解码的问题,本文提出了一种硬件上基于dm642进行设计、软件上基于mpeg-4进行编解码的视频编解码器实现方案,mpeg-4视频和音频压缩编码标准的应用,有效地解决了视频数据量大与数字存贮媒体和通信带宽小的矛盾,大大提高了视频通信的交互能力和编码效率,解码后处理过程中采用的去振铃滤波器提高了接收数据质量.

该文以ti公司tms320dm642dsp为核心处理器设计实现了一个符合mpeg标准的低码率实时视频编码器。主要特色是:提出并实现了中心三步搜索和菱形搜索相结合的方法进行快速运动搜索:提出并实现了一种新的全零块预先判别方法;针对dsp系统结构以及指令特点对编码过程中的运算密集部分进行专门优化。实验表明.该文提出的快速运动搜索算法性能优于中心三步搜索算法。全零块预先判别机制在保证图像质量的同时能有效减小运算量并降低码率。

介绍了xilinx公司的32位软核处理器microblaze的结构,分析了国家音视频编解码标准avs的技术特点,简述了软硬件协同设计的avs视频编码器的体系结构及软硬件划分,重点阐述了在此体系中microblaze处理器及相应软件的设计。

机载视频图像种类多样,要求编码器具备很高的处理能力和灵活性。设计一种基于dsp和fpga的编码器,通过对h.264/avc算法进行适当修改,实现dsp和fpga并行流水处理。fpga作为dsp的协处理器,完成子像素运动估计和帧内模式预测功能,大大降低了dsp的计算负载。经测试,设计的编码器可以实现1路高清视频(hdtv:1280×720,30帧/s)或者2路标清视频(sdtv:720×576,25帧/s)的实时编码。同时,fpga还可以完成遥测数据与视频码流的融合打包传输,简化了机上遥测系统的设计。

文章提出了一种基于tms320dm642的视频会议终端硬件设计方案。视频会议终端主要包括dm642最小系统的设计,电源模块的设计,视频输入模块的设计,usb传输接口模块的设计等,同时介绍了终端硬件的调试过程。终端通过硬件对采集的视频进行压缩编码,减轻了电脑cpu的工作负担,能够传输高清晰度的视频信号,实现了便携、稳定、灵活的移动视频会议终端平台。

rohm面向监视摄像头和家居安全设备、汽车行驶记录仪等安装有相机模块的设备,开发了内置雾图像处理功能的视频编码器icbu6521kv。

针对现场可编程门阵列(fpga)平台,提出可重构视频编码(rvc)的硬件实现方案.为提高系统吞吐量和功能单元(fu)的可重用及可扩性,提出分层的、多颗粒度并存的、可重用的功能单元设计方法;为重构的简单性及降低实现复杂度,提出在功能单元之间采用不同的存储结构作为数据连接方式.最终实现支持h.264/avc和avs的全i帧可重构视频编码器.结果表明,该编码器在xilinxvirtex-5330上能够分别实现h.264/avc标准下25帧及avs标准下37帧1920×1080视频的实时编码,比2个标准单独的设计实现代价降低了33%.

用数字信号处理(dsp)实现视频图像的压缩编码应用灵活、扩展性好,可以克服专用芯片视频编码器和现场可编程门阵列(fpga)视频编码器的一些局限性,有广泛的应用前景。论述了基于dsp64xx的视频编码器硬件平台,着重分析了编码器外部存储器高速数字信号的信号完整性问题,对数据线、地址线的信号传输波形进行了仿真、分析,并详细阐述了dsp视频编码器软件框架结构和软件优化策略。该编码器已在工程中广泛使用,性能稳定可靠。

介绍一种基于ti公司达芬奇系列dspdm648设计的网络视频服务器的方案,因为其简化的bom清单和灵活的软件设计,具有很高的实用价值。

文辑创建者

我要分享 >

职位:房地产土地资产评估师

擅长专业:土建 安装 装饰 市政 园林

相关编辑

文辑推荐

知识推荐

百科推荐