可重复触发单稳态触发器在检测电路中应用

2024-09-20

"555"定时器是一种数模混合中的规模集成电路,它使用灵活、方便,被广泛应用于脉冲的产生、整形、定时和延迟等电路中。由其构成的可重复触发单稳态触发器,能比较方便地得到持续时间更长的输出脉冲宽度。本文介绍了由555定时器构成的可重复触发单稳态触发器的电路构成与工作原理,以人体心律监视电路中失落脉冲检测为例,讨论了其在信号检测电路中的应用,说明在实际生产中,只要将其各个功能加以综合应用,便可得到许多实用电路。

针对目前高校教学中555单稳态触发器设计和调试实验电路中存在的问题,提出运用先进eda技术完成单稳态触发器设计和仿真研究的方法,使电路设计过程具有快捷性、高效性和准确性,完成符合质量要求的555单稳态触发器的设计。

基于数字电路和通信电路中,常常需要单稳态触发器,特别是要求延时功能时间可以调节的单稳态触发器,采用可编程控制器的这一特殊方法来设计这一触发器,通过调整可编程控制器构成的单稳态触发器的时间常数,巧妙地完成了这一功能。该设计具有设计简单,完成方便,延迟精度高,延迟范围不受限制,延迟时间用软件就可调试,不需要对电路重新组装的特点。

编辑推荐下载

提出555时基电路的输出信号与输入信号之间具有时序特征.根据反映时序特征的状态转换图及单稳态触发器的工作特点,系统地研究了555单稳态触发器的设计方法,分析了外加触发信号的输入方式、电平幅度、持续时间要求、rc电路定时单元的接法及电容的充放电过程,并发现了一些新的设计方案.multisim仿真及实际硬件验证证明了所提出设计方案的正确性.

热门文档 可重复触发单稳态触发器在检测电路中应用

1 第九节门电路和触发器 电子电路通常分模拟电子电路和数字电子电路两大类。前面介绍的放大电路属于第 一类,电路中的工作信号是连续变化的电信号(模拟信号)。数字电路的基本工作信号是 二进制的数字信号,它在时间上和数值上是离散的,即不是连续渐变的,而且只有0和 1两个基本数字,反映在电路上就是低电平和高电平两种状态。因此在稳态时,电路中 的半导体器件都是工作在开、关状态。数字电路是由几种最基本的单元电路组成的。在 这些基本单元中,对元件的精度要求不高,只要在工作时能够可靠地区分0和1两种状 态就可以了。数字电路中研究的主要问题是输入信号的状态(0或1)和输出信号的状态 (0或1)之间的关系,即所谓逻辑关系,采用的数学工具是逻辑代数。 一、逻辑代数基础 在逻辑代数中变量具有二值性,即只有两个可能的取值“0”和“1”。 (一)基本的逻辑运算 逻辑代数的基本

介绍了一种低抖动、快前沿高电压重复率触发器,输出参数为:重复率可达100pulse/s,输出时延约225ns,抖动约1ns,前沿约26ns,脉宽约70ns,高阻负载上电脉冲的峰值可达-40kv,重复率为50pulse/s时,峰值可达-51kv,单次工作时的峰值可达-60kv。该触发器主要由控制单元、高压供电单元与脉冲形成单元构成,脉冲形成单元采用了低电感电容对负载快放电的结构,建立开关为氢闸流管。实验发现,氢闸流管存在微导通状态,开关的通道电阻及维持的时间与开关极间的电势差有关;电势差越高,通道电阻越小,微导通状态维持的时间越长。此外,氢闸流管的导通性能受灯丝加热电源的影响明显,当加热电压较低时,氢闸流管导通缓慢,延时与抖动较大,当加热电压过高时,氢闸流管易于发生自击穿。

设计了一种在现场可编程逻辑阵列(fpga)内可供配置的触发器电路结构.主要特点是:不需要浪费fpga内组合逻辑的资源,就可以独立配置出56种全部常用类型的d触发器电路或锁存器电路;以fpga在配置简单时序电路时增加50%面积的代价降低了配置为复杂时序电路时70%的延时和90%的面积.同时针对xilinxvirtex系列fpga动态重配置速度较慢的缺点,在触发器电路中加入了抓捕与写回电路;提出了通过硬件电路来实现重配置状态保存和写回的方法.与xilinxvirtex器件完全用软件实现的方法相比,加快了fpga动态重配置电路的速度.

触发器作为连接组合逻辑电路和时序逻辑电路这两部分的桥梁,在整个数字电路中起着承上启下的作用。因而,对于触发器的掌握显得非常重要。本文针对触发器的教学提出了总分式,循序渐进、由浅入深,对比,抓住内在联系,把握重点等几条原则,希望能给大家学习触发器带来帮助。

精华文档 可重复触发单稳态触发器在检测电路中应用

为获得快前沿的高电压脉冲,分析了电容放电型触发器的电路,利用简化的等效电路研究了放电回路参数和气体开关的火花通道电阻、电感对触发脉冲上升时间的影响。分析了电压波在高阻抗负载上形成触发脉冲的过程,讨论了不同置地元件对输出波形的影响。在此基础上,给出了快前沿的电容放电型触发器的基本设计原则,并完成了30与100kv快前沿触发器的设计。结果表明,30kv触发器输出脉冲的前沿约12ns,高阻抗负载上的幅值可达44kv;100kv触发器输出脉冲的前沿约10ns,高阻抗负载上的幅值可达170kv。

提出一种基于单电子晶体管的新型电路结构——r-set结构,并从r-set结构的反相器着手对该结构电路的工作原理和性能进行了分析.构造出基于r-set结构的或非门、一位数值比较器、sr锁存器和d触发器.通过对各电路进行spice仿真,验证了各电路的正确性.最后对r-set和互补型set2种结构的d触发器进行性能比较,得出r-set结构的d触发器具有结构简单,功耗低,延时小的特点.

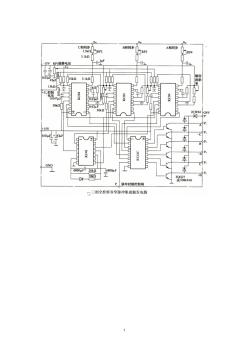

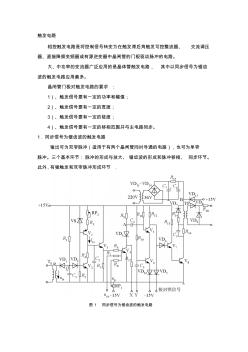

触发电路 相控触发电路是将控制信号转变为在触发滞后角触发可控整流器、交流调压 器、直接降频变频器或有源逆变器中晶闸管的门极驱动脉冲的电路。 大、中功率的变流器广泛应用的是晶体管触发电路,其中以同步信号为锯齿 波的触发电路应用最多。 晶闸管门极对触发电路的要求: 1)、触发信号要有一定的功率和幅值; 2)、触发信号要有一定的宽度; 3)、触发信号要有一定的陡度; 4)、触发信号要有一定的移相范围并与主电路同步。 1.同步信号为锯齿波的触发电路 输出可为双窄脉冲(适用于有两个晶闸管同时导通的电路),也可为单窄 脉冲。三个基本环节:脉冲的形成与放大、锯齿波的形成和脉冲移相、同步环节。 此外,有强触发和双窄脉冲形成环节. 图1同步信号为锯齿波的触发电路 1)脉冲形成环节 v4、v5—脉冲形成 v7、v8—脉冲放大 控制电压uco加在v4基极上 脉冲前沿由

为了实现可逆逻辑电路的可测性设计,充分利用可逆逻辑电路中存在的输出引脚,提出一种可逆逻辑电路测试综合方法.通过定义可逆逻辑门的可观性值和可控性值的计算方法,对可逆逻辑电路的可测性进行建模;通过插入观察点,制定了可逆组合逻辑电路可测性实现方案;通过对现有的d触发器进行改造并构建全新的扫描d触发器,制定了可逆时序电路的可测性逻辑实现方案;最后分析了扫描d触发器的工作特点,规范了测试步骤,建立一种可逆逻辑电路的测试综合方法.实验结果表明,与现有方法相比,文中方法插入观察点代价平均增加不到1%,但电路的可观性平均能得到24%的改善.

最新文档 可重复触发单稳态触发器在检测电路中应用

提出六值代数,建立五值电路三要素理论(信号,网络和负载理论),作为定量研究五值电路的数学工具。在此基础上,首先用δ展开法由五值门函数设计了五值门电路的元件级结构。接着由d触发器的特征方程设计了动态和静态五值d触发器的二种电路结构。计算机模拟验证了上述理论和依此理论设计的电路的正确性。

本文设计了时钟边沿可控双边沿触发器,在传统的双边沿触发器内部增加时钟控制电路,实现对单个时钟边沿的控制。同时,提出了基于隔态封锁技术的时序电路设计方法,可封锁时钟信号中所有冗余边沿的触发行为。hspice模拟与能耗分析证明,本文设计的电路不仅能够封锁所有的冗余时钟边沿的触发,而且可以简化组合电路部分的设计,从而实现更低的系统功耗。

采用当前成熟的两种抗单粒子翻转锁存器构成了主从d触发器,在d触发器加固设计中引入了时钟加固技术,对输出也采用了加固设计。仿真对比显示本设计的加固效果优于国内同类设计。

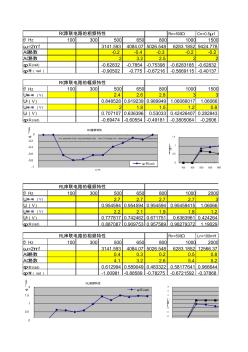

rn=500ωcn=0.5μf f/hz10030050065080010001500 ω=2πf3141.5934084.075026.5486283.18529424.778 ab格数-0.2-0.4-0.3-0.2-0.2 ac格数23.22.522 φ实(rad)-0.62832-0.7854-0.75398-0.6283185-0.62832 φ理(rad)-0.90502-0.775-0.67216-0.5669115-0.40137 f/hz10030050065080010001500 ur峰-峰(v)2.42.62.833 ur(v)0.8485280.9192390.9899491.060660171.06066 uc峰-峰(v)21.81.51.2

为了探索多输入时序逻辑电路的简便实现方法,介绍了基于数据选择器和d触发器的多输入时序逻辑电路设计技术。即将d触发器和数据选择器进行组合,用触发器的现态作为数据选择器选择输入变量、数据选择器的输出函数作为触发器的d输入信号,构成既有存储功能又有数据选择功能的多输入端时序网络。由触发器的现态选择输入变量、所选择的输入变量决定触发器的次态转换方向。该方法适合实现互斥多变量时序逻辑电路,且在设计过程中不需要进行函数化简。

提出了一种用相变器件作为可擦写存储单元的具有掉电数据保持功能的触发器电路.该触发器由四部分组成:具有恢复掉电时数据的双置位端触发器dff、上电掉电监测置位电路(poweron/offreset)、相变存储单元的读写电路(readwrite)和reset/set信号产生电路,使之在掉电时能够保存数据,并在上电时完成数据恢复.基于0.13μmsmic标准cmos工艺,采用candence软件对触发器进行仿真,掉电速度达到0.15μs/v的情况下,上电时可以在30ns内恢复掉电时的数据状态.

对于广播发射机的日常维护工作,准确的判断发射机的故障点是快速处理发射机故障的先决条件。在dx-200型中波发射机中,一些故障由于故障指示瞬间消失或者故障指示不能覆盖到给维护人员判断故障位置、缩短处理故障的时间带来了负担。以调制编码板的电源故障指示电路为载体,本文用d触发器设计出一种稳定可靠的故障点记忆电路,在实际运行中把故障现场保持记忆,留给维护人员,大大提高了故障处理效率。

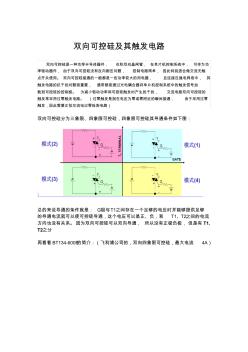

双向可控硅及其触发电路 双向可控硅是一种功率半导体器件,也称双向晶闸管,在单片机控制系统中,可作为功 率驱动器件,由于双向可控硅没有反向耐压问题,控制电路简单,因此特别适合做交流无触 点开关使用。双向可控硅接通的一般都是一些功率较大的用电器,且连接在强电网络中,其 触发电路的抗干扰问题很重要,通常都是通过光电耦合器将单片机控制系统中的触发信号加 载到可控硅的控制极。为减小驱动功率和可控硅触发时产生的干扰,交流电路双向可控硅的 触发常采用过零触发电路。(过零触发是指在电压为零或零附近的瞬间接通,由于采用过零 触发,因此需要正弦交流电过零检测电路) 双向可控硅分为三象限、四象限可控硅,四象限可控硅其导通条件如下图: 总的来说导通的条件就是:g极与t1之间存在一个足够的电压时并能够提供足够 的导通电流就可以使可控硅导通,这个电压可以是正、负,和t1、t2之间的电流

文辑创建者

我要分享 >

职位:消防主管工程师

擅长专业:土建 安装 装饰 市政 园林

相关编辑

文辑推荐

知识推荐

百科推荐