斯密特触发器简易数字相位计设计

2024-05-28

基于斯密特触发器精确波形变换特性实现对两路输入信号的波形转换与校正,利用STC5410单片机计算输出,设计一款简易数字相位计,完成对两路信号相位差的测量,具有测量精度高,成本低,外围电路简单等优点.

针对城市道路照明led改造中半功率节电应用的特点,提出了一种基于光控和长延时开关的led路灯控制方案,利用光敏电阻、555时基电路和cd4060二进制计数器实现了控制电路的设计;实验结果表明:本方案简单可行,实用可靠。

编辑推荐下载

1 第九节门电路和触发器 电子电路通常分模拟电子电路和数字电子电路两大类。前面介绍的放大电路属于第 一类,电路中的工作信号是连续变化的电信号(模拟信号)。数字电路的基本工作信号是 二进制的数字信号,它在时间上和数值上是离散的,即不是连续渐变的,而且只有0和 1两个基本数字,反映在电路上就是低电平和高电平两种状态。因此在稳态时,电路中 的半导体器件都是工作在开、关状态。数字电路是由几种最基本的单元电路组成的。在 这些基本单元中,对元件的精度要求不高,只要在工作时能够可靠地区分0和1两种状 态就可以了。数字电路中研究的主要问题是输入信号的状态(0或1)和输出信号的状态 (0或1)之间的关系,即所谓逻辑关系,采用的数学工具是逻辑代数。 一、逻辑代数基础 在逻辑代数中变量具有二值性,即只有两个可能的取值“0”和“1”。 (一)基本的逻辑运算 逻辑代数的基本

热门文档 斯密特触发器简易数字相位计设计

触发器作为连接组合逻辑电路和时序逻辑电路这两部分的桥梁,在整个数字电路中起着承上启下的作用。因而,对于触发器的掌握显得非常重要。本文针对触发器的教学提出了总分式,循序渐进、由浅入深,对比,抓住内在联系,把握重点等几条原则,希望能给大家学习触发器带来帮助。

利用sqlserver2000数据库自身的触发器功能,设计了一种数据实时传输的方式,简化了网络通信模块的程序设计,提高了系统的可扩展性和可维护性。

该文介绍了数字电路中冗余模块的概念及去除冗余模块对低功耗设计的意义,并进一步将这一低功耗设计思想应用于基于三值时钟的三值双边沿触发器的设计中,对其进行了简化设计和模拟,指出简化设计后的触发器比原触发器结构简单,且模拟结果表明其逻辑功能正确且能有效地降低功耗。

容侵技术提供了系统在遭受攻击的情况下连续提供服务的能力。容侵系统的根本触发点在于根据监控到的服务器运行状态,提供不同策略的安全保护。借鉴网络安全问题与生物免疫系统的惊人相似性(两者都要在不断变化的环境中维持系统的稳定性),基于人工免疫思想,结合数据挖掘技术knn,设计了一个基于免疫分类算法的容侵系统触发器,详细描述了其设计思想、主要算法、工作原理和模块结构,并对其进行了仿真实验。相比现有ids主要通过监控已知的攻击方式和手段实现监控不同,此系统监控服务器自身性能,而与攻击方式无关。仿真结果表明,该触发器可以对其所在的服务器状态进行实时地、动态地监控,容侵系统可以根据该触发器所反应出的当前服务器状态,提供不同级别的服务和执行不同策略的安全保护,具有一定的实用价值。

采用当前成熟的两种抗单粒子翻转锁存器构成了主从d触发器,在d触发器加固设计中引入了时钟加固技术,对输出也采用了加固设计。仿真对比显示本设计的加固效果优于国内同类设计。

精华文档 斯密特触发器简易数字相位计设计

用传统时序逻辑电路设计方法,可实现利用d触发器对2n进制循环码产生电路的设计。但设计过程较繁琐,容易出错。针对上述问题提出了一种利用d触发器设计2n进制循环码产生电路的简单方法。

在深入研究能量回收和门控时钟技术的基础上,提出了能量回收时钟发生器和触发器的新型设计方案。该方案在smic0.35μmcmos标准工艺下,利用spectre软件进行仿真。仿真结果表明,采用能量回收技术后,新型结构的功耗比传统结构下降约42%;采用门控时钟技术后,新型结构的功耗比传统结构下降约65%。

为获得快前沿的高电压脉冲,分析了电容放电型触发器的电路,利用简化的等效电路研究了放电回路参数和气体开关的火花通道电阻、电感对触发脉冲上升时间的影响。分析了电压波在高阻抗负载上形成触发脉冲的过程,讨论了不同置地元件对输出波形的影响。在此基础上,给出了快前沿的电容放电型触发器的基本设计原则,并完成了30与100kv快前沿触发器的设计。结果表明,30kv触发器输出脉冲的前沿约12ns,高阻抗负载上的幅值可达44kv;100kv触发器输出脉冲的前沿约10ns,高阻抗负载上的幅值可达170kv。

最新文档 斯密特触发器简易数字相位计设计

本文设计了时钟边沿可控双边沿触发器,在传统的双边沿触发器内部增加时钟控制电路,实现对单个时钟边沿的控制。同时,提出了基于隔态封锁技术的时序电路设计方法,可封锁时钟信号中所有冗余边沿的触发行为。hspice模拟与能耗分析证明,本文设计的电路不仅能够封锁所有的冗余时钟边沿的触发,而且可以简化组合电路部分的设计,从而实现更低的系统功耗。

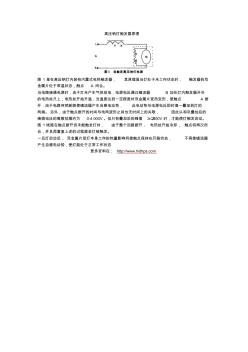

高压钠灯触发器原理 图1是在高压钠灯内装有内置式电热触发器,其原理是当灯处于未工作状态时,触发器的双 金属片处于常温状态,触点a闭合。 当电路接通电源时,由于灯未产生气体放电,电源电压通过镇流器b加在灯内触发器开关 的电热丝尺上,电热丝开始升温,当温度达到一定程度时双金属片受热变形,使触点a断 开,由于电路突然断路使镇流器产生自感电动势,此电动势与电源电压即时值∽叠加到灯的 两端。另外,由于触点断开的时间与电网波形之间也无时间上的关联,因此以和巩叠加后的 峰值电压的离散范围约为0-4000v。但只有叠加后的峰值≥2500v时,才能使灯触发启动。 图1线路在触点断开但未能触发灯时,由于整个回路断开,电热丝开始冷却,触点将再次闭 合,并且再重复上述的过程直至灯被触发。 一旦灯启动后,双金属片受灯本身工作的热量影响将使触点保持在开路状态,不再使镇流器

介绍了一种低抖动、快前沿高电压重复率触发器,输出参数为:重复率可达100pulse/s,输出时延约225ns,抖动约1ns,前沿约26ns,脉宽约70ns,高阻负载上电脉冲的峰值可达-40kv,重复率为50pulse/s时,峰值可达-51kv,单次工作时的峰值可达-60kv。该触发器主要由控制单元、高压供电单元与脉冲形成单元构成,脉冲形成单元采用了低电感电容对负载快放电的结构,建立开关为氢闸流管。实验发现,氢闸流管存在微导通状态,开关的通道电阻及维持的时间与开关极间的电势差有关;电势差越高,通道电阻越小,微导通状态维持的时间越长。此外,氢闸流管的导通性能受灯丝加热电源的影响明显,当加热电压较低时,氢闸流管导通缓慢,延时与抖动较大,当加热电压过高时,氢闸流管易于发生自击穿。

针对目前高校教学中555单稳态触发器设计和调试实验电路中存在的问题,提出运用先进eda技术完成单稳态触发器设计和仿真研究的方法,使电路设计过程具有快捷性、高效性和准确性,完成符合质量要求的555单稳态触发器的设计。

针对面向对象数据库(oodb)触发器的实现机制进行研究,对oodb触发器事件进行分类。利用面向对象语言中事件结构,实现oodb触发器事件的注册、订阅及引发过程。在db4o引擎基础上给出一种oodb触发器实现方案。

传统施密特型压控振荡器存在输入电压下限值较高、最高振荡频率较低等缺点。针对这两个问题,文中介绍了一种具有新型充放电电路结构的施密特型压控振荡器,并在0.18μm工艺下对电路进行了仿真。结果表明,相对于传统施密特型压控振荡器,新型振荡器输入电压下限值有所下降,且最高振荡频率也有明显提升。

数字系统中,常常需要施密特触发器,特别是回差电压很大,并且可以根据需要随意调节的施密特触发器。采用可编程控制器状态转移图和功能指令中的比较指令这一特殊方法设计了此款施密特触发器,通过调整可编程控制器构成的施密特触发器的上限门坎电平和下限门坎电平,巧妙地完成了回差电压很大、回差电压可随意调节这一功能。该设计具有设计简单,完成方便,不需要对电路重新组装的特点。

提出了一种用相变器件作为可擦写存储单元的具有掉电数据保持功能的触发器电路.该触发器由四部分组成:具有恢复掉电时数据的双置位端触发器dff、上电掉电监测置位电路(poweron/offreset)、相变存储单元的读写电路(readwrite)和reset/set信号产生电路,使之在掉电时能够保存数据,并在上电时完成数据恢复.基于0.13μmsmic标准cmos工艺,采用candence软件对触发器进行仿真,掉电速度达到0.15μs/v的情况下,上电时可以在30ns内恢复掉电时的数据状态.

通过对传统触发器结构和旁道攻击密码系统原理的研究,提出一种具有抗差分能量攻击性能的jk触发器设计方案。首先,根据双轨预充逻辑电路交替处于预充阶段与求值阶段的特点,结合触发器的特征方程,推导出具有抗差分能量攻击性能的jk触发器的状态方程;然后,根据场效应管宽长比对数据传输速率的影响,采用灵敏放大型逻辑,得到相应的触发器电路结构。hspice模拟验证表明,所设计电路具有正确的逻辑功能。与传统jk触发器比较,该结构具有显著的抗差分能量攻击性能。

利用muller_c单元,设计一种异步保存及互锁存储单元结构,该结构采用状态锁存机制和增加节点电容方法,能有效防止单粒子翻转效应的发生,同时也可提高电路抗单粒子瞬变和多节点扰动效应的能力。在0.18μm工艺条件下用此结构设计的d触发器,面积为1422μm2,动态功耗为0.42mw,建立时间为0.2ns,保持时间为0.03ns。实验结果表明:利用触发器链验证电路,在时钟频率为20mhz时,单粒子let翻转阈值为31mev·cm2/mg,比双互锁存储单元结构的抗单粒子能力提高40%。

文辑创建者

我要分享 >

职位:停车场智能化管理工程

擅长专业:土建 安装 装饰 市政 园林

相关编辑

文辑推荐

知识推荐

百科推荐