PCB板技术

高速PCB设计中的串扰分析与控制物理分析与验证对于确保复杂、高速PCB板级和系统级设计的成功起到越来越关键的作用。本文将介绍在信号完整性分析中抑制和改善信号串扰的方法,以及电气规则驱动的高速PCB板布线技术实现信号串扰控制的设计策略

-

选择特殊符号

选择搜索类型

请输入搜索

高速PCB设计中的串扰分析与控制物理分析与验证对于确保复杂、高速PCB板级和系统级设计的成功起到越来越关键的作用。本文将介绍在信号完整性分析中抑制和改善信号串扰的方法,以及电气规则驱动的高速PCB板布线技术实现信号串扰控制的设计策略

高速PCB设计规则通常分两种:物理规则和电气规则。所谓物理规则是指设计工程师指定基于物理尺寸的某些设计规则,比如线宽为4Mi1,线与线之间的间距为4Mi1,平行走线长度为4Mi1等。而电气规则是指有关电特性或者电性能方面的设计规则,如布线延时控制在Ins到2ns之间,某一个PCB线上的串扰总量小于70mV等等.

定义清楚了物理规则和电气规则就可以进一步探讨高速布线器。目前市场上基于物理规则(物理规则驱动)的高速布线器有AutoActive RE布线器、CCT布线器、B1azeRouter布线器和Router Editor布线器,实际上这些布线器都是物理规则驱动的自动布线器,也就是说这些布线器只能够自动满足设计工程师指定的物理尺寸方面的要求,而并不能够直接受高速电气的物理尺寸方面的要求,而并不能够直接受高速电气 规则所驱动。

电气规则直接驱动的高速布线器对于确保高速设计信号完整性来说非常重要,设计工程师总是最先得到电气规则而且设计规范也是电气规则,换句话说我们的设计最终必须满足的是电气规则而不是物理规则,最终的物理设计实现满足设计的电气规则要求才是最本质的。物理规则仅仅是元器件厂商或者是设计工程师自己对电气规则作的一种转换,我们总是期望这种 转换是对等的,是一一对应的。而实际情况并非如 此。

以采用LVDS芯片来完成高速率(高达777.76Mbps)、长距离(长达loom)的数据传输为例,由于LVDS技术的信号摆幅是3500,那么通常的设计规范总是要求信号线上总的串扰值应该小于等于信号摆幅的20%,也就是串扰的总量最大350mV X20%=700,这就是电气规则,其中20%的百分比取决于LVDS的噪声容限,可以从参考手册上获得。

对于IS_Synthesizer来说,设计工程师只要指定该LVDS信号线上的串扰值大小,布线时就能够自动调整和细化来确保满足电性能方面的要求,在布线过程中会自动考虑周围所有信号线对该LVDS信号的影响。而对基于物理规则驱动的布线器来说,首先需要进行一些假想的分析和考虑,设计工程师总是认为信号之间的串扰仅仅取决于平行信号之间并行走线的长度,所以可以在高速电路设计的前端环境中做一些假想的分析,比如可以假定并行走线的长度是2.5mil,然后分析它们之间的串扰,这个值可能并不是70mV,但是可以根据得到的结论来进一步调整并行走线的长度,假如恰好当并行走线的长度是某一个确定的值如7mi1时信号之间的串扰值基本上就是70mV,那么设计工程师就认为只要保证差分线对并行走线的长度控制在7mi1范围以内就能够满足这样的电气特性要求(信号串扰值控制在70mV以内),于是在实际的物理PCB布局布线时设计工程师就得到了这样一个高速PCB设计的物理规则,常规的高速布线器都可以确保满足这种物理尺寸方面的要求。

这里会存在两个问题:首先,规则的转换并不等同,首先信号之间的串扰并非唯一由并行信号之间走线的长度来决定,还取决于信号的流向、并行线段所处的位置,以及有无匹配等多种因素,而这些因素可能很难预料,甚至不可能在实际的物理实现之前充分地进行考虑。所以经过这样的转换之后,并不能够确保在满足这些物理规则的情况下,同时能够满足原始的电气规则。这也是为什么上述的这些高速布线器在满足规则的情况下,PCB系统仍然不能正常工作的很重要的一个原因。其次,在这些规则转换时几乎不可能同时考虑多方面的影响,如在考虑信号串扰时很难同时考虑到周围所有相关信号线的影响。这两方面的情况就决定了基于物理规则的高速布线器在高速、高复杂度的PCB系统设计中将存在很大的问题,而真正基于电气规则驱动的高速PCB布线器就较好地解决了这方面的问题。

数字系统对时序要求严格,为了满足信号时序的要求,对PCB上的信号走线长度进行调整已经成为PCB设计工作的一部分。调整走线长度包括两个方面:相对的和绝对的。

所谓相对的就是要求走线长度保持一致,保证信号同步到达若干个接收器。有时候在PCB上的一组信号线之间存在着相关性,比如总线,就需要对其长度进行校正,因为需要信号在接收端同步。其调整方法就是找出其中最长的那根走线,然后将其他走线调整到等长。

而绝对的要求是控制两个器件之间的走线延迟为某一个值,比如器件A、B之间的延迟为Ins,而这样的要求往往由高速电路设计者提出,而由PCB工程师去实现。要满足这个要求,就必须知道信号的传播速度c但需要注意,信号传播速度是和PCB的材料、走线的结构、走线的宽度、过孔等因素相关的。知道了信号传播速度,就知道了要求的走线延迟对应的走线长度。

当前,日渐精细的半导体工艺使得晶体管尺寸越来越小,因而器件的信号跳变沿也就越来越快,从而导致高速数字电路系统设计领域信号完整性问题以及电磁兼容性方面的问题日趋严重。信号完整性问题主要包括传输线效应,如反射、时延、振铃、信号的过冲与下冲以及信号之间的串扰等,其中信号串扰最为复杂,涉及因素多、计算复杂而难以控制。所以今天的电子产品设计迫切需要区别于传统设计环境、设计流程和设计方法的全新思路、流程、方法和技术。

EDA技术已经研发出一整套高速PCB和电路板级系统的设计分析工具和方法学,这些技术涵盖高速电路设计分析的方方面面:静态时序分析、信号完整性分析、EMI/EMC设计、地弹反射分析、功率分析以及高速布线器。同时还包括信号完整性验证和Sig'n-Off,设计空间探测、互联规划、电气规则约束的互联综合,以及专家系统等技术方法的提出也为高效率更好地解决信号完整性问题提供了可能。信号完整性分析与设计是最重要的高速PCB板级和系统级分析与设计手段,在硬件电路设计中扮演着越来越重要的作用,这里将讨论信号完整性问题中的信号串扰。

在当今社会,电子技术高度发达,无处不存在电子产品,电子产品中都有电路板的身影,他是电子产品的载体或者核心部分,今天就和大家谈谈,电路板的制作流程。首先根据项目的要求设计原理图,也就是线路该怎么走,电子...

从头开始1.绘制元件库2.绘制原理图3.绘制封装库4.导入网络表5.布板6.画线最后把PCB做好了后一般都要做成GERBER文件投板到PCB厂家厂家的步骤是1)单面板工艺流程 开料磨边→钻孔→外层图形...

展开全部防潮和隔绝氧化,这个主要靠表面涂刷保护漆。还有就是防止大电流产生高温,这个主要是靠加大铜箔面积,增加表面焊锡,增加散热孔,在发热严重的元器件上加装散热片和热风扇等。然后就是机械保护,这个主要是...

信号之间由于电磁场的相互祸合而产生的不期望的噪声电压信号称为信号串扰。串扰超出一定的值将可能引发电路误动作从而导致系统无法正常工作。解决串扰问题问题可以从以下几个方面考虑:

通常在器件选型的时候,在满足设计规范的同时尽量选择慢速的器件,并且避免不同种类的信号混合使用,因为快速变换的信号对慢变换的信号有潜在的串扰危险。

为高速信号提供包地是解决串扰问题的一个有效途径。然而,包地会导致布线量增加,使原本有限的布线区域更加拥挤。另外,地线屏蔽要达到预期目的,地线上接地点间距很关键,一般小于信号变化沿长度的两倍。同时地线也会增大信号的分布电容,使传输线阻抗增大,信号沿变缓。

合理设置布线层和布线间距,减小并行信号长度,缩短信号层与平面层的间距,增大信号线间距,减小并行信号线长度(在关键长度范围内),这些措施都可以有效减小串扰。

为不同速率的信号设置不同的布线层,并合理设置平面层,也是解决串扰的好方法。

如果传输线近端或远端终端阻抗与传输线阻抗匹配,也可以大大减小串扰的幅度。串扰分析的目的是为了在PCB实现中迅速地发现、定位和解决串扰问题。一般的仿真工具与环境中仿真分析与PCB板布线环境互相独立,布线结束后进行串扰分析,得到串扰分析报告,推导出新的布线规则并且重新布线,再分析修正,这样设计的反复比较多。通过仿真分析可以看到,实际的串扰结果都不相同,并且差距很大。因此,一个好的工具应该不 仅能够分析串扰,并且能够应用串扰规则进行布线。另外,一般的布线工具仅限于物理规则驱动,对控制串扰的布线只能通过设定线宽和线间距,以及最大并行走线长度等物理规则来约束。采用信号完整性分析和设计工具集ICX可以支持真正意义上的电气规则 驱动布线,其仿真分析和布线在一个环境下完成,在仿真时可以设定电气规则和物理规则,在布线的同时自动计算过冲、串扰等信号完整性要素,并根据计算的结果自动修正布线。这样的布线速度快,而且真正符合实际的电气性能要求。

高速PCB板级、系统级设计是一个复杂的过程,包括信号串扰在内的信号完整性问题带来设计观念、设计思路、设计流程以及设计手段的变革。确保在高速系统设计中迅速发现问题、解决问题,并且指导在新的设计中预防问题的出现已经成为今天高速系统设计的主流。

pcb板加工合同

pcb板加工合同

pcb板加工合同

第 1 页 共 20 页 竭诚为您提供优质文档 /双击可除 pcb板加工合同 篇一: pcb 板采购合同 篇一: pcb 采购合同 -090204(1) 电路板承揽定作合同 订货方 (以下简称甲方 ): 供货方 (以下简称乙方 ): 经甲乙双方友好协商,乙方按照甲方的要求,承揽电路 板一批 ,双方经协议 ,订立本合同 : 一、承揽工艺要求及含税 费用:二、交货日期: 20XX/2/11 ,付款方式:收 30%定金, 余款 70%货到款清 ; 四、甲方收到货后,如有质量问题,应于七日内通知乙 方,逾期视为质量合格,乙方恕不负责甲方损失;乙方收 到甲方质量问题通知后,应于七日内处理完质量问题 (包括修复不良,无法修复免费更换) ,否则甲方有权取消 合同,并追回相关款项。 五、乙方仅对甲方所供资料负保密义务 ,如交货出现品 质问题导致甲方无法使用 ,乙方负责赔偿费用不大于该批电 第 2 页

PCB板检验标准

PCB板检验标准

PCB板检验标准

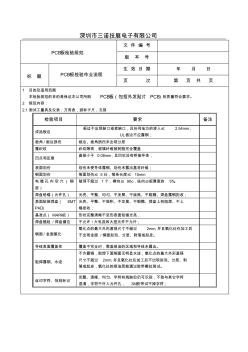

深圳市三诺技展电子有限公司 PCB板检验规范 文 件 编 号 版 本 号 标 题 PCB板检验作业流程 生 效 日 期 年 月 日 页 次 第 页 共 页 1 目的及适用范围 本检验规范的目的是保证本公司所购 PCB板(包括外发贴片 PCB)的质量符合要求。 2 规范内容: 2.1测试工量具及仪表:万用表,游标卡尺,孔规 检验项目 要求 备注 成品板边 板边不出现缺口或者缺口,且任何地方的渗入≤ 2.54mm; UL板边不应露铜; 板角 / 板边损伤 板边、板角损伤未出现分层 露织纹 织纹隐现,玻璃纤维被树脂完全覆盖 凹点和压痕 直径小于 0.08mm,且凹坑没有桥接导体; 表面划伤 划伤未使导体露铜、划伤未露出基材纤维; 铜面划伤 每面划伤≤ 5 处,每条长度≤ 15mm 电镀孔 内空穴( 铜 层) 破洞不超过 1 个,横向≤ 90o,纵向≤板厚度的 5%。 焊盘铅锡(元件孔) 光亮、

双面PCB板与单面PCB板的区别,在于单面板线路只在PCB板的一面,而双面PCB的线路则可以在PCB板的两个面中,中间用过孔将双面的PCB板线路连接起来。

双面PCB板的参数双面PCB板制作与单面PCB板除了制作的流程不一样外,还多一沉铜工艺,也就是将双面线路导通的工艺。

《多层PCB板的制备方法》涉及PCB(printedcircuitboard,印刷电路板)板,特别是涉及一种多层PCB板的制备方法 。

PCB板夹具是一种PCB板的检测装置,尤其是一种PCB板检测时的夹具。

具有设置于机座上可前后滑移的固定座、设置于固定座上的前挡杆和后挡杆,所述前挡杆与固定座固定连接,后挡杆与固定座滑动连接,在前挡杆上设置有由翘压板和顶板组成的PCB板夹头,PCB板夹头的中部与前挡杆销接,在机座的前端设置有顶杆装置,所述顶杆装置由固定安装于机座上的底座和设置于底座上的顶杆组成,在固定座移动到最前端时,顶杆装置的顶杆与顶板相抵。本实用新型结构简单,对PCB板的可以方便快捷地实施夹持,提高了工作效率,同时对PCB板的夹持也比较稳固,确保了摄像机对PCB板进行拍摄图像的清晰,从而提高了PCB板检测的准确度。