DS1302文献

DS1302实时时钟电路

DS1302实时时钟电路

DS1302实时时钟电路

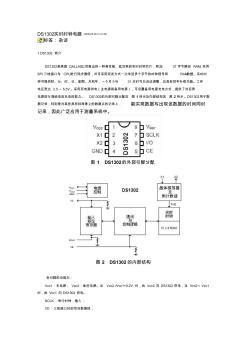

DS1302实时时钟电路 (2009-05-05 21:21:45) 标签:杂谈 1 DS1302 简介 DS1302是美国 DALLAS公司推出的一种高性能、低功耗的实时时钟芯片,附加 31字节静态 RAM,采用 SPI 三线接口与 CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号和 RAM数据。实时时 钟可提供秒、分、时、日、星期、月和年,一个月小与 31天时可以自动调整,且具有闰年补偿功能。工作 电压宽达 2.5 ~5.5V。采用双电源供电(主电源和备用电源),可设置备用电源充电方式,提供了对后背 电源进行涓细电流充电的能力。 DS1302的外部引脚分配如 图 1所示及内部结构如 图 2所示。DS1302用于数 据记录,特别是对某些具有特殊意义的数据点的记录上, 能实现数据与出现该数据的时间同时 记录,因此广泛应用于测量系统中。 图 1 DS1302的外部引脚分配

基于Atmega16和DS1302的数码管时钟设计

基于Atmega16和DS1302的数码管时钟设计

基于Atmega16和DS1302的数码管时钟设计

在日常生活中和自动控制系统中,时间与实时数据采集都需要时钟。DS1302是一款优秀的实时时钟芯片。介绍了DS1302的主要工作原理和编程思路,给出了AVR单片机Atmega16与DS1302的硬件接口电路和软件程序设计。系统在Proteus平台上进行了软、硬件交互仿真,实现了数码管时钟设计。