sop封装

- SOP封装是一种元件封装形式,常见的封装材料有:塑料、陶瓷、玻璃、金属等,基本采用塑料封装.,应用范围很广,主要用在各种集成电路中。

-

选择特殊符号

选择搜索类型

请输入搜索

SOP封装的应用范围很广,而且以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等在集成电路中都起到了举足轻重的作用。像主板的频率发生器就是采用的SOP封装。

SOP封装的应用范围很广,而且以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等在集成电路中都起到了举足轻重的作用。像主板的频率发生器就是采用的SOP封装。

SOP(Small Out-Line Package小外形封装)是一种很常见的元器件形式。表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L 字形)。材料有塑料和陶瓷两种。始于70年代末期。由1980 年代以前的通孔插装(PTH)型态,主流产品为DIP(Dual In-Line Package),进展至1980 年代以SMT(Surface Mount Technology)技术衍生出的SOP(Small Out-Line Package)、SOJ(Small Out-Line J-Lead)、PLCC(Plastic Leaded Chip Carrier)、QFP(Quad Flat Package)封装方式,在IC 功能及I/O 脚数逐渐增加后,1997 年Intel 率先由QFP 封装方式更新为BGA(Ball Grid Array,球脚数组矩阵)封装方式,除此之外,近期主流的封装方式有CSP(Chip Scale Package 芯片级封装)及Flip Chip(覆晶)。

1968~1969年菲利浦公司就开发出小外形封装(SOP).以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

SOP-8封装带微动开关启动和LED输出指示的PWM驱动集成电路IC有哪些?型号是?

您这是简单的扫地机器人电路。根据您画的图它有可能是一个sop8封装的单片机。但也不排除其他芯片的可能,根据您画的图即便有输出,电机也无法转动和反转。建议,可以用轻触开关,单片机,制作简易的扫地机器人。

标书在所有封口的缝隙处都应该盖章,没有说明的照样盖章。

圖1: 每次使用前,先檢查 保養卡的保養日期 是否過期,若過期, 應立即停止使用,通 &nb...

SOP(Small Out-Line Package小外形封装)是一种很常见的元器件形式。表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L 字形)。材料有塑料和陶瓷两种。始于70年代末期。由1980 年代以前的通孔插装(PTH)型态,主流产品为DIP(Dual In-Line Package),进展至1980 年代以SMT(Surface Mount Technology)技术衍生出的SOP(Small Out-Line Package)、SOJ(Small Out-Line J-Lead)、PLCC(Plastic Leaded Chip Carrier)、QFP(Quad Flat Package)封装方式,在IC 功能及I/O 脚数逐渐增加后,1997 年Intel 率先由QFP 封装方式更新为BGA(Ball Grid Array,球脚数组矩阵)封装方式,除此之外,近期主流的封装方式有CSP(Chip Scale Package 芯片级封装)及Flip Chip(覆晶)。

1968~1969年菲利浦公司就开发出小外形封装(SOP)。以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

按封装形式分:普通双列直插式,普通单列直插式,小型双列扁平,小型四列扁平,圆形金属,体积较大的厚膜电路等。

按封装体积大小排列分:最大为厚膜电路,其次分别为双列直插式,单列直插式,金属封装、双列扁平、四列扁平为最小。

按两引脚之间的间距分:普通标准型塑料封装,双列、单列直插式一般多为2.54±0.25 mm,其次有2mm(多见于单列直插式)、1.778±0.25mm(多见于缩型双列直插式)、1.5±0.25mm,或1.27±0.25mm(多见于单列附散热片或单列V型)、1.27±0.25mm(多见于双列扁平封装)、1±0.15mm(多见于双列或四列扁平封装)、0.8±0.05~0.15mm(多见于四列扁平封装)、0.65±0.03mm(多见于四列扁平封装)。

按双列直插式两列引脚之间的宽度分:一般有7.4~7.62mm、10.16mm、12.7mm、15.24mm等数种。

按双列扁平封装两列之间的宽度分(包括引线长度):一般有6~6.5±mm、7.6mm、10.5~10.65mm等。

按四列扁平封装40引脚以上的长×宽一般有:10×10mm(不计引线长度)、13.6×13.6±0.4mm(包括引线长度)、20.6×20.6±0.4mm(包括引线长度)、8.45×8.45±0.5mm(不计引线长度)、14×14±0.15mm(不计引线长度)等。2100433B

SOP标准样板

SOP标准样板

SOP标准样板

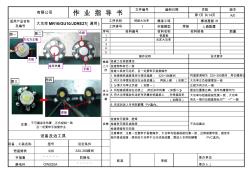

文件编号 版本 A/0 焊接大功率 標准工時 標准產能 /H 1 作業類型 人員配置 序号 材料名称 数量 1 铝基板 2 光匠大功率 3 4 5 设备,工装名称 型号 设定条件 恒温烙铁 936 320-380度间 手指套  ̄ ̄ ̄ ̄ ̄ 防静电 静电环 OWS20A  ̄ ̄ ̄ ̄ ̄ 不良品截出 本工 序作 業 有限公司 作 业 指 导 书 编制日期 页数第1页 共14页 适用产品名称 及编号 大功率MR16/GU10/JDRE27( 通用 ) 工序名称 工序排号 焊接 材料编号 材料规格 操作说明 技术要求 1.检查烙铁溫度是否为規定溫度: 320~380度间 将温度调制为 320~380度间,用仪器测试 2.将大功率摆放固定在治具底模上 ,再装上模 (如图二)大功率正负极要摆放一致 檢查 上工 序 检查工位表面清洁 检查物料有无一致 检查工具有无完好、且一定要带手指套操作 6.完成后

工程部SOP

工程部SOP

工程部SOP

凤都国际大酒店 标准操作程序 --- 工程部 部门 : 工程部 工作岗位 : 值班工程师、主管 任务编码 : SOP-30-001 任务 : 项目申请程序 设备要求 : 做什么 如何做 为什么 一、申请所需外包工程项目。 二、外包项目合同编写。 三、外包项目施工监督。 四、项目工作验收完结。 一、项目过程: 1. 由值班工程师、主管提出外包 项目、书面报告,上报副总工 程师。 2. 副总工程师经审核后,将同意 外包的项目请示总工程师。必 需征得总工程师同意,才能开 始对外询价。 3. 由主管编写外包项目任务书, 详列工程范围、施工草图、验 收条件和材料数量、规格,并 上报 值班工程 师全面复核 签 认,值班工程师应对项目技术 标准负责。 4. 副总工程师对外包项目任务书 进行估价后,报总工程师。 5. 副总工程师组织三家以上询 价,将询价结果报财务总监、 总经理。 6. 副

采用BGA技术封装的内存,可以使内存在体积不变的情况下,内存容量提高两到三倍,BGA与TSOP相比,具有更小体积,更好的散热性能和电性能。BGA封装技术使每平方英寸的存储量有了很大提升,采用BGA封装技术的内存产品在相同容量下,体积只有TSOP封装的三分之一;与传统TSOP封装方式相比,BGA封装方式有更加快速有效的散热途径。

采用BGA技术封装的内存,可以使内存在体积不变的情况下内存容量提高两到三倍,BGA与TSOP相比,具有更小的体积,更好的散热性能和电性能。BGA封装技术使每平方英寸的存储量有了很大提升,采用BGA封装技术的内存产品在相同容量下,体积只有TSOP封装的三分之一;另外,与传统TSOP封装方式相比,BGA封装方式有更加快速和有效的散热途径。

BGA封装的I/O端子以圆形或柱状焊点按阵列形式分布在封装下面,BGA技术的优点是I/O引脚数虽然增加了,但引脚间距并没有减小反而增加了,从而提高了组装成品率;虽然它的功耗增加,但BGA能用可控塌陷芯片法焊接,从而可以改善它的电热性能;厚度和重量都较以前的封装技术有所减少;寄生参数(电流大幅度变化时,引起输出电压扰动)减小,信号传输延迟小,使用频率大大提高;组装可用共面焊接,可靠性高。

采用BGA技术封装的内存, 可以使内存在体积不变的情况下内存容量提高两到三倍, BGA与TSOP相比, 具有更小的体积, 更好的散热性能和电性能。BGA封装技术使每平方英寸的存储量有了很大提升, 采用BGA封装技术的内存产品在相同容量下, 体积只有TSOP封装的三分之一;

另外, 与传统TSOP封装方式相比, BGA封装方式有更加快速和有效的散热途径。

BGA发展来的CSP封装技术正在逐渐展现它生力军本色, 金士顿、勤茂科技等领先内存制造商已经推出了采用CSP封装技术的内存产品。

CSP, 全称为Chip Scale Package, 即芯片尺寸封装的意思。作为新一代的芯片封装技术, 在BGA、TSOP的基础上, CSP的性能又有了革命性的提升。CSP封装可以让芯片面积与封装面积之比超过1:1.14,已经相当接近1:1的理想情况, 绝对尺寸也仅有32平方毫米, 约为普通的BGA的1/3, 仅仅相当于TSOP内存芯片面积的1/6。这样在相同体积下, 内存条可以装入更多的芯片, 从而增大单条容量。也就是说, 与BGA封装相比, 同等空间下CSP封装可以将存储容量提高三倍, 图4展示了三种封装技术内存芯片的比较, 从中我们可以清楚的看到内存芯片封装技术正向着更小的体积方向发展。CSP封装内存不但体积小, 同时也更薄, 其金属基板到散热体的最有效散热路径仅有0.2mm, 大大提高了内存芯片在长时间运行后的可靠性, 线路阻抗显著减小, 芯片速度也随之得到大幅度的提高。CSP封装的电气性能和可靠性也相比BGA、TOSP有相当大的提高。在相同的芯片面积下CSP所能达到的引脚数明显的要比TSOP、BGA引脚数多的多(TSOP最多304根,BGA以600根为限,CSP原则上可以制造1000根), 这样它可支持I/O端口的数目就增加了很多。

此外, CSP封装内存芯片的中心引脚形式有效的缩短了信号的传导距离, 其衰减随之减少, 芯片的抗干扰、抗噪性能也能得到大幅提升, 这也使得CSP的存取时间比BGA改善15%-20%。在CSP的封装 方式中, 内存颗粒是通过一个个锡球焊接在PCB板上, 由于焊点和PCB板的接触面积较大, 所以内存芯片在运行中所产生的热量可以很容易地传导到PCB板上并散发出去;而传统的TSOP封装方式, 内存芯片是通过芯片引脚焊在PCB板上的, 焊点和PCB板的接触面积较小, 使得芯片向PCB板传热就相对困难。CSP封装可以从背面散热, 且热效率良好, CSP的热阻为35℃/W, 而TSOP热阻40℃/W。

测试结果显示, 运用CSP封装的内存可使传导到PCB板上的热量高达88.4%, 而TSOP内存中传导到PCB板上的热量能为71.3%。另外由于CSP芯片结构紧凑, 电路冗余度低, 因此它也省去了很多不必要的电功率消耗, 致使芯片耗电量和工作温度相对降低。目前内存颗粒厂在制造DDR333和DDR400内存的时候均采用0.175微米制造工艺, 良品率比较低。而如果将制造工艺提升到0.15甚至0.13微米的话, 良品率将大大提高。而要达到这种工艺水平, 采用CSP封装方式则是不可避免的。因此CSP封装的高性能内存是大势所趋

这种高密度、小巧、扁薄的封装技术非常适宜用于设计小巧的手持式消费类电子装置, 如个人信息工具、手机、摄录一体机、以及数码相机。