公共阻抗文献

低压母线阻抗及相保阻抗

低压母线阻抗及相保阻抗

低压母线阻抗及相保阻抗

mΩ /m TMY 200 3(40×4)+1(40×4) 0.1119 250 3(40×4)+1(40×4) 0.1119 315 3(50×5)+1(50×5) 0.0728 400 3(63×6.3)+1(63×6.3) 0.0471 500 3(80×6.3)+1(63×6.3) 0.0383 630 3(80×8)+1(63×6.3) 0.031 800 3(100×8)+1(80×6.3) 0.0257 1000 3(125×10)+1(80×8) 0.0177 1250 3*2(100×10)+1(100× 10) 0.0109 1600 3*2(125×10)+1(125× 10) 0.0089 2000 3*2(125×10)+1(125× 10) 0.0089 变压器容 量KVA 母线规格 mm Rm D=150 D=250 D=350 mΩ /m mΩ /m mΩ

导线阻抗

导线阻抗

导线阻抗

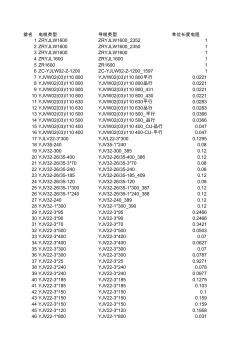

排名 电线类型 导线类型 单位长度电阻 1 ZRYJLW1600 ZRYJLW1600_2352 1 2 ZRYJLW1600 ZRYJLW1600_2350 1 3 ZRYJLW1600 ZRYJLW1600 1 4 ZRYJL1600 ZRYJL1600 1 5 ZR1600 ZR1600 1 6 ZC-YJLW02-Z-1200 ZC-YJLW02-Z-1200_1597 1 7 YJVW02(03)/110 800 YJVW02(03)/110 800平行 0.0221 8 YJVW02(03)/110 800 YJVW02(03)/110 800品行 0.0221 9 YJVW02(03)/110 800 YJVW02(03)/110 800_431 0.0221 10 YJVW02(03)/110 800 YJVW02(03)/110 800_430 0.0221 11 YJV