芯片制造--半导体工艺制程实用教程

本书是一本介绍半导体集成电路和器件制造技术的专业书籍, 在半导体领域享有很高的声誉。本书的讨论范围包括半导体工艺的每个阶段: 从原材料的制备到封装、 测试和成品运输, 以及传统的和现代的工艺。全书提供了详细的插图和实例, 每章包含回顾总结和习题, 并辅以丰富的术语表。

-

选择特殊符号

选择搜索类型

请输入搜索

本书是一本介绍半导体集成电路和器件制造技术的专业书籍, 在半导体领域享有很高的声誉。本书的讨论范围包括半导体工艺的每个阶段: 从原材料的制备到封装、 测试和成品运输, 以及传统的和现代的工艺。全书提供了详细的插图和实例, 每章包含回顾总结和习题, 并辅以丰富的术语表。

第1章 半导体产业

1.1 引言

1.2 一个产业的诞生

1.3 固态时代

1.4 集成电路

1.5 工艺和产品趋势

1.6 半导体产业的构成

1.7 生产阶段

1.8 微芯片制造过程发展的

60年

1.9 纳米时代

习题

参考文献

第2章 半导体材料和化学品的特性

2.1 引言

2.2 原子结构

2.3 元素周期表

2.4 电传导

2.5 绝缘体和电容器

2.6 本征半导体

2.7 掺杂半导体

2.8 电子和空穴传导

2.9 半导体生产材料

2.10 半导体化合物

2.11 锗化硅

2.12 衬底工程

2.13 铁电材料

2.14 金刚石半导体

2.15 工艺化学品

2.16 物质的状态

2.17 物质的性质

2.18 压力和真空

2.19 酸、 碱和溶剂

2.20 化学纯化和清洗

习题

参考文献

第3章 晶体生长与硅晶圆制备

3.1 引言

3.2 半导体硅制备

3.3 晶体材料

3.4 晶体定向

3.5 晶体生长

3.6 晶体和晶圆质量

3.7 晶圆准备

3.8 切片

3.9 晶圆刻号

3.10 磨片

3.11 化学机械抛光

3.12 背面处理

3.13 双面抛光

3.14 边缘倒角和抛光

3.15 晶圆评估

3.16 氧化

3.17 包装

3.18 工程化晶圆(衬底)

习题

参考文献

第4章 晶圆制造和封装概述

4.1 引言

4.2 晶圆生产的目标

4.3 晶圆术语

4.4 芯片术语

4.5 晶圆生产的基础工艺

4.6 薄膜工艺

4.7 晶圆制造实例

4.8 晶圆中测

4.9 集成电路的封装

4.10 小结

习题

参考文献

第5章 污染控制

5.1 引言

5.2 污染源

5.3 净化间的建设

5.4 净化间的物质与供给

5.5 净化间的维护

5.6 晶片表面清洗

习题

参考文献

第6章 生产能力和工艺良品率

6.1 引言

6.2 良品率测量点

6.3 累积晶圆生产良品率

6.4 晶圆生产良品率的制约因素

6.5 封装和最终测试良品率

6.6 整体工艺良品率

习题

参考文献

第7章 氧化

7.1 引言

7.2 二氧化硅层的用途

7.3 热氧化机制

7.4 氧化工艺

7.5 氧化后评估

习题

参考文献

第8章 十步图形化工艺流程--从表面

制备到曝光

8.1 引言

8.2 光刻工艺概述

8.3 光刻十步法工艺过程

8.4 基本的光刻胶化学

8.5 光刻胶性能的要素

8.6 光刻胶的物理属性

8.7 光刻工艺: 从表面准备到曝光

8.8 表面准备

8.9 涂光刻胶(旋转式)

8.10 软烘焙

8.11 对准和曝光

8.12 先进的光刻

习题

参考文献

第9章 十步图形化工艺流程--从显影到最终检验

9.1 引言

9.2 硬烘焙

9.3 刻蚀

9.4 湿法刻蚀

9.5 干法刻蚀

9.6 干法刻蚀中光刻胶的影响

9.7 光刻胶的去除

9.8 去胶的新挑战

9.9 最终目检

9.10 掩模版的制作

9.11 小结

习题

参考文献

第10章 下一代光刻技术

10.1 引言

10.2 下一代光刻工艺的挑战

10.3 其他曝光问题

10.4 其他解决方案及其挑战

10.5 晶圆表面问题

10.6 防反射涂层

10.7 高级光刻胶工艺

10.8 改进刻蚀工艺

10.9 自对准结构

10.10 刻蚀轮廓控制

习题

参考文献

第11章 掺杂

11.1 引言

11.2 扩散的概念

11.3 扩散形成的掺杂区和结

11.4 扩散工艺的步骤

11.5 淀积

11.6 推进氧化

11.7 离子注入简介

11.8 离子注入的概念

11.9 离子注入系统

11.10 离子注入区域的杂质浓度

11.11 离子注入层的评估

11.12 离子注入的应用

11.13 掺杂前景展望

习题

参考文献

第12章 薄膜淀积

12.1 引言

12.2 化学气相淀积基础

12.3 CVD的工艺步骤

12.4 CVD系统分类

12.5 常压CVD系统

12.6 低压化学气相淀积(LPCVD)

12.7 原子层淀积

12.8 气相外延

12.9 分子束外延

12.10 金属有机物CVD

12.11 淀积膜

12.12 淀积的半导体膜

12.13 外延硅

12.14 多晶硅和非晶硅淀积

12.15 SOS和SOI

12.16 在硅上生长砷化镓

12.17 绝缘体和绝缘介质

12.18 导体

习题

参考文献

第13章 金属化

13.1 引言

13.2 淀积方法

13.3 单层金属

13.4 多层金属设计

13.5 导体材料

13.6 金属塞

13.7 溅射淀积

13.8 电化学镀膜

13.9 化学机械工艺

13.10 CVD金属淀积

13.11 金属薄膜的用途

13.12 真空系统

习题

参考文献

第14章 工艺和器件的评估

14.1 引言

14.2 晶圆的电特性测量

14.3 工艺和器件评估

14.4 物理测试方法

14.5 层厚的测量

14.6 栅氧化层完整性电学测量

14.7 结深

14.8 污染物和缺陷检测

14.9 总体表面特征

14.10 污染认定

14.11 器件电学测量

习题

参考文献

第15章 晶圆制造中的商业因素

15.1 引言

15.2 晶圆制造的成本

15.3 自动化

15.4 工厂层次的自动化

15.5 设备标准

15.6 统计制程控制

15.7 库存控制

15.8 质量控制和ISO 9000认证

15.9 生产线组织架构

习题

参考文献

第16章 形成器件和集成电路的

介绍

16.1 引言

16.2 半导体器件的形成

16.3 可替换MOSFET按比例缩小的挑战

16.4 集成电路的形成

16.5 Bi MOS

16.6 超导体

习题

参考文献

第17章 集成电路的介绍

17.1 引言

17.2 电路基础

17.3 集成电路的类型

17.4 下一代产品

习题

参考文献

第18章 封装

18.1 引言

18.2 芯片的特性

18.3 封装功能和设计

18.4 引线键合工艺

18.5 凸点或焊球工艺示例

18.6 封装设计

18.7 封装类型和技术小结

习题

参考文献

术语表

本书是一本介绍半导体集成电路和器件制造技术的专业书籍, 在半导体领域享有很高的声誉。本书的讨论范围包括半导体工艺的每个阶段: 从原材料的制备到封装、 测试和成品运输, 以及传统的和现代的工艺。全书提供了详细的插图和实例, 每章包含回顾总结和习题, 并辅以丰富的术语表。

第六版修订了微芯片制造领域的新进展, 讨论了用于图形化、 掺杂和薄膜步骤的先进工艺和尖端技术, 使隐含在复杂的现代半导体制造材料与工艺中的物理、 化学和电子的基础信息更易理解。

本书的主要特点是避开了复杂的数学问题介绍工艺技术内容, 并加入了半导体业界的新成果, 可以使读者了解工艺技术发展的趋势。

led芯片就是发光二极管芯片,也就是你说的照明芯片。本质上来说,就是一个pn节,电子和空穴在pn节的耗尽层复合,复合后多出的能量以光子的形式发射出去,也就是发光照明了。这个产业分成三个部分:外延生长,...

我想你是要问芯片应用了半导体的什么性质了吧,由于半导体可以进行不同掺杂性形成pn结,使其具有整流特性实现电路的与或非门,即逻辑表达。对于集成电路来讲,最底下的一层叫衬底(一般为P型半导体),是参与集成...

1、半导体是技术与资本密集产业,更重要的是专利,许多专利已被先进者卡位,后进入产业者动辄侵权,被告的很惨,中芯与台积电,Intel与VIA(威盛)都是例子 2、台湾半导体产业进入得早,与政府有计划的辅...

多芯片半导体激光器光纤耦合设计

多芯片半导体激光器光纤耦合设计

多芯片半导体激光器光纤耦合设计

应用ZEMAX光学设计软件模拟了一种多芯片半导体激光器光纤耦合模块,将12支808nm单芯片半导体激光器输出光束耦合进数值孔径0.22、纤芯直径105μm的光纤中,每支半导体激光器功率10 W,光纤输出端面功率达到116.84W,光纤耦合效率达到97.36%,亮度达到8.88MW/(cm2·sr)。通过ZEMAX和ORIGIN软件分析了光纤对接出现误差以及单芯片半导体激光器安装出现误差时对光纤耦合效率的影响,得出误差对光纤耦合效率影响的严重程度从大到小分别为垂轴误差、轴向误差、角向误差。

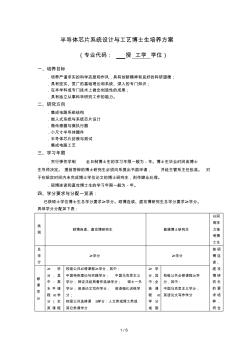

半导体芯片系统设计与工艺博士生培养方案

半导体芯片系统设计与工艺博士生培养方案

半导体芯片系统设计与工艺博士生培养方案

1 / 6 半导体芯片系统设计与工艺博士生培养方案 (专业代码: 授 工学 学位) 一、培养目标 .培养严谨求实的科学态度和作风,具有创新精神和良好的科研道德; .具有坚实、宽广的基础理论和系统、深入的专门知识; .在本学科或专门技术上做出创造性的成果; .具有独立从事科学研究工作的能力。 二、研究方向 .集成电路系统结构 .嵌入式系统与系统芯片设计 .微传感器与微执行器 .小尺寸半导体器件 .半导体芯片封装与测试 .集成电路工艺 三、学习年限 .实行弹性学制 全日制博士生的学习年限一般为-年。博士生毕业时间由博士 生导师决定。 提前答辩的博士研究生必须向系提出书面申请, 并经主管系主任批准。 对 于在规定时间内未完成博士学位论文的博士研究生,则作肄业处理。 .硕博连读和直攻博士生的学习年限一般为-年。 四、学分要求与分配一览表: 已获硕士学位博士生总学分要求≥学分。硕博连读、直攻博研究

本书是一本介绍半导体集成电路和器件制造技术的专业书籍,在半导体领域享有很高的声誉。本书的范围包括半导体工艺的每个阶段:从原材料的制备到封装、测试和成品运输,以及传统的和现代的工艺。全书提供了详细的插图和实例,每章包含回顾总结和习题,并辅以丰富的术语表。第六版修订了微芯片制造领域的新进展,讨论了用于图形化、掺杂和薄膜步骤的先进工艺和尖端技术,使隐含在复杂的现代半导体制造材料和工艺中的物理、化学和电子的基础知识更易理解。

本书的主要特点是避开了复杂的数学问题介绍工艺技术内容;加入了半导体业界的新成果,可以使读者了解工艺技术发展的趋势。

1 The Semiconductor Industry 1

Introduction 1

Birth of an Industry 1

The Solid-State Era 3

Integrated Circuits (ICs) 4

Process and Product Trends 5

Moore’s Law 6

Decreasing Feature Size 6

Increasing Chip and Wafer Size 8

Reduction in Defect Density 9

Increase in Interconnection Levels 10

The Semiconductor Industry Association Roadmap 10

Chip Cost 11

Industry Organization 11

Stages of Manufacturing 12

Six Decades of Advances in Microchip Fabrication Processes 14

The Nano Era 16

Review Topics 17

References 17

2 Properties of Semiconductor Materials and Chemicals 19

Introduction 19

Atomic Structure 19

The Bohr Atom 19

The Periodic Table of the Elements 20

Electrical Conduction 23

Conductors 23

Dielectrics and Capacitors 23

Resistors 24

Intrinsic Semiconductors 24

Doped Semiconductors 25

Electron and Hole Conduction 26

Carrier Mobility 28

Semiconductor Production Materials 29

Germanium and Silicon 29

Semiconducting Compounds 29

Silicon Germanium 31

Engineered Substrates 31

Ferroelectric Materials 31

Diamond Semiconductors 32

Process Chemicals 32

Molecules, Compounds, and Mixtures 32

Ions 33

States of Matter 34

Solids, Liquids, and Gases 34

Plasma State 34

Properties of Matter 34

Temperature 34

Density, Specic Gravity, and Vapor Density 35

Pressure and Vacuum 36

Acids, Alkalis, and Solvents 37

Acids and Alkalis 37

Solvents 38

Chemical Purity and Cleanliness 38

Safety Issues 38

The Material Safety Data Sheet 39

Review Topics 39

References 39

3 Crystal Growth and Silicon Wafer Preparation 41

Introduction 41

Semiconductor Silicon Preparation 41

Silicon Wafer Preparation Stages 42

Crystalline Materials 42

Unit Cells 43

Poly and Single Crystals 43

Crystal Orientation 44

Crystal Growth 45

Czochralski Method 45

Liquid-Encapsulated Czochralski 47

Float Zone 47

Crystal and Wafer Quality 49

Point Defects 49

Dislocations 50

Growth Defects 50

Wafer Preparation 51

End Cropping 51

Diameter Grinding 51

Crystal Orientation, Conductivity, and Resistivity Check 51

Grinding Orientation Indicators 52

Wafer Slicing 53

Wafer Marking 54

Rough Polish 54

Chemical Mechanical Polishing 55

Backside Processing 55

Double-Sided Polishing 56

Edge Grinding and Polishing 56

Wafer Evaluation 56

Oxidation 57

Packaging 57

Wafer Types and Uses 57

Reclaim Wafers 57

Engineered Wafers (Substrates) 57

Review Topics 58

References 58

4 Overview of Wafer Fabrication and Packaging 59

Introduction 59

Goal of Wafer Fabrication 59

Wafer Terminology 59

Chip Terminology 61

Basic Wafer-Fabrication Operations 63

Layering 63

Patterning 64

Circuit Design 66

Reticle and Masks 68

Doping 69

Heat Treatments 69

Example Fabrication Process 72

Wafer Sort 74

Packaging 75

Summary 75

Review Topics 76

References 76

5 Contamination Control 77

Introduction 77

The Problem 77

Contamination-Caused Problems 80

Contamination Sources 81

General Sources 81

Air 81

Clean Air Strategies 82

Cleanroom Workstation Strategy 83

Tunnel or Bay Concept 85

Micro- and Mini-Environments 86

Temperature, Humidity, and Smog 87

Cleanroom Construction 88

Construction Materials 88

Cleanroom Elements 89

Personnel-Generated Contamination 93

Process Water 94

Process Chemicals 96

Equipment 99

Cleanroom Materials and Supplies 99

Cleanroom Maintenance 100

Wafer-Surface Cleaning 100

Particulate Removal 102

Wafer Scrubbers 102

High-Pressure Water Cleaning 103

Organic Residues 103

Inorganic Residues 103

Chemical-Cleaning Solutions 104

General Chemical Cleaning 104

Oxide Layer Removal 105

Room Temperature and Ozonated Chemistries 106

Water Rinsing 108

Drying Techniques 110

Contamination Detection 112

Review Topics 112

References 113

6 Productivity and Process Yields 115

Overview 115

Yield Measurement Points 115

Accumulative Wafer-Fabrication Yield 116

Wafer-Fabrication Yield Limiters 117

Number of Process Steps 118

Wafer Breakage and Warping 118

Process Variation 119

Mask Defects 120

Wafer-Sort Yield Factors 120

Wafer Diameter and Edge Die 121

Wafer Diameter and Die Size 122

Wafer Diameter and Crystal Defects 122

Wafer Diameter and Process Variations 123

Die Area and Defect Density 124

Circuit Density and Defect Density 125

Number of Process Steps 125

Feature Size and Defect Size 125

Process Cycle Time 125

Wafer-Sort Yield Formulas 125

Assembly and Final Test Yields 128

Overall Process Yields 128

Review Topics 129

References 130

7 Oxidation 131

Introduction 131

Silicon Dioxide Layer Uses 131

Surface Passivation 131

Doping Barrier 132

Surface Dielectric 132

Device Dielectric (MOS Gates) 133

Device Oxide Thicknesses 134

Thermal Oxidation Mechanisms 134

Influences on the Oxidation Rate 137

Thermal Oxidation Methods 140

Horizontal Tube Furnaces 140

Temperature Control System 141

Source Cabinet 143

Vertical Tube Furnaces 143

Rapid Thermal Processing 146

High-Pressure Oxidation 149

Oxidant Sources 151

Oxidation Processes 154

Preoxidation Wafer Cleaning 154

Postoxidation Evaluation 155

Surface Inspection 156

Oxide Thickness 156

Oxide and Furnace Cleanliness 156

Thermal Nitridation 156

Review Topics 157

References 157

8 The Ten-Step Patterning Process—Surface Preparation to Exposure 161

Introduction 161

Overview of the Photomasking Process 162

Ten-Step Process 165

Basic Photoresist Chemistry 167

Photoresist 167

Photoresist Performance Factors 169

Resolution Capability 169

Adhesion Capability 170

Process Latitude 171

Pinholes 172

Particle and Contamination Levels 173

Step Coverage 173

Thermal Flow 173

Comparison of Positive and Negative Resists 173

Physical Properties of Photoresists 175

Solids Content 175

Viscosity 175

Surface Tension 176

Index of Refraction 176

Storage and Control of Photoresists 176

Light and Heat Sensitivity 176

Viscosity Sensitivity 177

Shelf Life 177

Cleanliness 177

Photomasking Processes—Surface Preparation to Exposure 178

Surface Preparation 178

Particle Removal 178

Dehydration Baking 178

Wafer Priming 179

Spin Priming 180

Vapor Priming 180

Photoresist Application (Spinning) 181

The Static Dispense Spin Process 181

Dynamic Dispense 183

Moving-Arm Dispensing 183

Manual Spinners 183

Automatic Spinners 184

Edge Bead Removal 185

Backside Coating 185

Soft Bake 185

Convection Ovens 186

Manual Hot Plates 187

In-Line, Single-Wafer Hot Plates 187

Moving-Belt Hot Plates 187

Moving-Belt Infrared Ovens 188

Microwave Baking 188

Vacuum Baking 188

Alignment and Exposure 189

Alignment and Exposure Systems 189

Exposure Sources 191

Alignment Criteria 191

Aligner Types 193

Postexposure Bake 196

Advanced Lithography 198

Review Topics 198

References 198

9 The Ten-Step Patterning Process—Developing to Final Inspection 201

Introduction 201

Development 201

Positive Resist Development 201

Negative Resist Development 203

Wet Development Processes 203

Dry (or Plasma) Development 206

Hard Bake 207

Hard-Bake Methods 207

Hard-Bake Process 207

Develop Inspect 208

Develop Inspect Reject Categories 209

Develop Inspect Methods 209

Causes for Rejecting at the Develop Inspection Stage 211

Etch 212

Wet Etching 212

Etch Goals and Issues 212

Incomplete Etch 212

Overetch and Undercutting 213

Selectivity 214

Wet-Spray Etching 214

Silicon Wet Etching 214

Silicon Dioxide Wet Etching 215

Aluminum-Film Wet Etching 216

Deposited-Oxide Wet Etching 216

Silicon Nitride Wet Etching 216

Vapor Etching 217

Dry Etch 217

Plasma Etching 218

Etch Rate 220

Radiation Damage 220

Selectivity 220

Ion-Beam Etching 222

Reactive Ion Etching 222

Resist Effects in Dry Etching 223

Resist Stripping 223

Wet Chemical Stripping of Nonmetallized Surfaces 224

Wet Chemical Stripping of Metallized Surfaces 225

Dry Stripping 225

Post–Ion Implant and Plasma Etch Stripping 226

New Stripping Challenges 226

Final Inspection 227

Mask Making 227

Summary 229

Review Topics 229

References 230

10 Next Generation Lithography 233

Introduction 233

Challenges of Next Generation Lithography 233

High-Pressure Mercury Lamp Sources 235

Excimer Lasers 236

Extreme Ultraviolet 236

X-Rays 237

Electron Beam or Direct Writing 238

Numerical Aperture of a Lens 240

Other Exposure Issues 241

Variable Numerical Aperture Lenses 242

Immersion Exposure System 242

Amplified Resist 242

Contrast Effects 243

Other Resolution Challenges and Solutions 244

Off-Axis Illumination 245

Lens Issues and Reection Systems 245

Phase-Shift Masks 245

Optical Proximity Corrected or Optical Process Correction 245

Annular-Ring Illumination 246

Pellicles 247

Surface Problems 248

Resist Light Scattering 248

Subsurface Reectivity 248

Antireective Coatings 249

Standing Waves 249

Planarization 251

Photoresist Process Advances 252

Multilayer Resist or Surface Imaging 252

Silylation or DESIRE Process 254

Polyimide Planarization Layers 255

Etchback Planarization 256

Dual-Damascene Process 256

Chemical Mechanical Polishing 256

Slurry 259

Polishing Rates 259

Planarity 260

Post-CMP Clean 261

CMP Tools 261

CMP Summary 262

Reow 262

Image Reversal 262

Contrast Enhancement Layers 262

Dyed Resists 264

Improving Etch Denition 264

Lift-Off Process 264

Self-Aligned Structures 264

Etch Prole Control 266

Review Topics 266

References 266

11 Doping 269

Introduction 269

The Diffusion Concept 269

Formation of a Doped Region and Junction 271

The N-P Junction 272

Doping Process Goals 273

Graphical Representation of Junctions 273

Concentration versus Depth Graphs 273

Lateral Diffusion 273

Same-Type Doping 275

Diffusion Process Steps 275

Deposition 275

Dopant Sources 278

Drive-In Oxidation 280

Oxidation Effects 281

Introduction to Ion Implantation 281

Concept of Ion Implantation 283

Ion-Implantation System 284

Implant Species Sources 284

Ionization Chamber 284

Mass Analyzing or Ion Selection 284

Acceleration Tube 286

Wafer Charging 286

Beam Focus 287

Neutral Beam Trap 287

Beam Scanning 287

End Station and Target Chamber 289

Ion-Implant Masks 290

Dopant Concentration in Implanted Regions 291

Crystal Damage 292

Annealing and Dopant Activation 292

Channeling 293

Evaluation of Implanted Layers 294

Uses of Ion Implantation 295

The Future of Doping 297

Review Topics 297

References 298

12 Layer Deposition 299

Introduction 299

Film Parameters 301

Chemical Vapor Deposition Basics 302

Basic CVD System Components 303

CVD Process Steps 305

CVD System Types 305

Atmospheric-Pressure CVD Systems 306

Horizontal-Tube Induction-Heated APCVD 306

Barrel Radiant-Induction-Heated APCVD 307

Pancake Induction-Heated APCVD 307

Continuous Conduction-Heated APCVD 308

Horizontal Conduction-Heated APCVD 309

Low-Pressure Chemical Vapor Deposition 309

Horizontal Conduction-Convection-Heated LPCVD 309

Ultra-High Vacuum CVD 310

Plasma-Enhanced CVD (PECVD) 310

High-Density Plasma CVD 312

Atomic Layer Deposition 313

Vapor-Phase Epitaxy 315

Molecular Beam Epitaxy 315

Metalorganic CVD 317

Deposited Films 318

Deposited Semiconductors 318 2100433B

《半导体芯片制造技术》全面系统地介绍了半导体芯片制造技术,内容包括半导体芯片制造概述、多晶半导体的制备、单晶半导体的制备、晶圆制备、薄膜制备、金属有机物化学气相沉积、光刻、刻蚀、掺杂及封装。书中简要介绍了半导体芯片制造的基本理论基础,系统介绍了多晶半导体、单晶半导体与晶圆的制备,详细介绍了薄膜制备、光刻与刻蚀及掺杂等工艺。由于目前光电产业的不断发展,对于化合物半导体的使用越来越多,《半导体芯片制造技术》以半导体硅材料芯片制造为主,兼顾化合物半导体材料芯片制造,比如在介绍薄膜制备工艺中,书中用单独的一章介绍了如何通过金属有机物化学气相沉积来制备化合物半导体材料薄膜。《半导体芯片制造技术》针对高职高专学生的特点,以"实用为主、够用为度"为原则,系统地介绍了半导体芯片制造技术。《半导体芯片制造技术》可作为微电子、光电子、光伏、电子等相关专业高职高专的教材,也可作为相关专业学生和技术人员的自学参考用书。