精品文献

138译码器

EDA:4-16译码器电路的设计

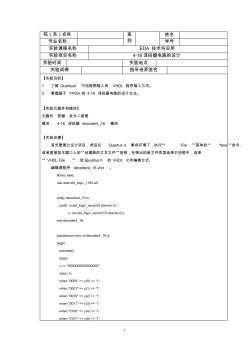

1 院(系)名称 班 别 姓名 专业名称 学号 实验课程名称 EDA 技术与应用 实验项目名称 4-16译码器电路的设计 实验时间 实验地点 实验成绩 指导老师签名 【实验目的】 1. 了解 QuartusII 中电路图输入和 VHDL 程序输入方式。 2. 掌握基于 FPGA 的 4-16 译码器电路的设计方法。 【实验元器件和模块】 元器件:按键、发光二极管 模块: 4-16 译码器 decoder4_16 模块 【实验步骤】 首先要建立设计项目,然后在 Quartus II 集成环境下,执行“ File ”菜单的“ New”命令, 或者直接按主窗口上的“创建新的文本文件”按钮,在弹出的新文件类型选择对话框中,选择 “ VHDL File ”,进入Quartus II 的 VHDL 文本编辑方式。 编辑源程序 decoder4_16.vhd 。 library ieee; use

高速BCH编码译码器的设计

高速BCH编码译码器的设计

高速BCH编码译码器的设计

针对闪存(flash)因制造工艺的不断提高而导致其内部数据区随机错误不断增加的现象,设计并实现一种高速BCH编码译码器,通过BCH编码技术对flash中的随机错误进行纠错,以达到错误检测与纠错的目的。实验结果显示优化设计的BCH(4 224,4 096)编码译码器可以工作在25 MHz的工作频率下,其单页数据(512 Byte)的纠错能力从普遍的3 bit提高到15 bit,从而提高了flash数据存储与读取的可靠性。