CMOS逻辑电路

- CMOS逻辑电路代表互补的金属氧化物半导体(Complementary Metal-Oxide-Semiconductor),它指的是一种特殊类型的电子集成电路(IC)。

-

选择特殊符号

选择搜索类型

请输入搜索

CMOS是单词的首字母缩写,代表互补的金属氧化物半导体(Complementary Metal-Oxide-Semiconductor),它指的是一种特殊类型的电子集成电路(IC)。集成电路是一块微小的硅片,它包含有几百万个电子元件。术语IC隐含的含义是将多个单独的集成电路集成到一个电路中,产生一个十分紧凑的器件。在通常的术语中,集成电路通常称为芯片,而为计算机应用设计的IC称为计算机芯片。

虽然制造集成电路的方法有多种,但对于数字逻辑电路而言CMOS是主要的方法。桌面个人计算机、工作站、视频游戏以及其它成千上万的其它产品都依赖于CMOS集成电路来完成所需的功能。当我们注意到所有的个人计算机都使用专门的CMOS芯片,如众所周知的微处理器,来获得计算性能时, CMOS IC的重要性就不言而喻了。CMOS之所以流行的一些原因为:

·逻辑函数很容易用CMOS电路来实现。

·CMOS允许极高的逻辑集成密度。其含义就是逻辑电路可以做得非常小,可以制造在极小的面积上。

·用于制造硅片CMOS芯片的工艺已经是众所周知,并且CMOS芯片的制造和销售价格十分合理。

这些特征及其它特征都为CMOS成为制造IC的主要工艺提供了基础。

CMOS可以作为学习在电子网络中如何实现逻辑功能的工具。CMOS它允许我们用简单的概念和模型来构造逻辑电路。而理解这些概念只需要基本的电子学概念。

CMOS逻辑门电路的系列及主要参数:

1.CMOS逻辑门电路的系列

CMOS集成电路诞生于20世纪60年代末,经过制造工艺的不断改进,在应用的广度上已与TTL平分秋色,它的技术参数从总体上说,已经达到或接近TTL的水平,其中功耗、噪声容限、扇出系数等参数优于TTL。CMOS集成电路主要有以下几个系列。

(1)基本的CMOS--4000系列。

这是早期的CMOS集成逻辑门产品,工作电源电压范围为3~18V,由于具有功耗低、噪声容限大、扇出系数大等优点,已得到普遍使用。缺点是工作速度较低,平均传输延迟时间为几十ns,最高工作频率小于5MHz。

(2)高速的CMOS--HC(HCT)系列。

该系列电路主要从制造工艺上作了改进,使其大大提高了工作速度,平均传输延迟时间小于10ns,最高工作频率可达50MHz。HC系列的电源电压范围为2~6V。HCT系列的主要特点是与TTL器件电压兼容,它的电源电压范围为4.5~5.5V。它的输入电压参数为VIH(min)=2.0V;VIL(max)=0.8V,与TTL完全相同。另外,74HC/HCT系列与74LS系列的产品,只要最后3位数字相同,则两种器件的逻辑功能、外形尺寸,引脚排列顺序也完全相同,这样就为以CMOS产品代替TTL产品提供了方便。

(3)先进的CMOS--AC(ACT)系列

该系列的工作频率得到了进一步的提高,同时保持了CMOS超低功耗的特点。其中ACT系列与TTL器件电压兼容,电源电压范围为4.5~5.5V。AC系列的电源电压范围为1.5~5.5V。AC(ACT)系列的逻辑功能、引脚排列顺序等都与同型号的HC(HCT)系列完全相同。

2.CMOS逻辑门电路的主要参数

CMOS门电路主要参数的定义同TTL电路,下面主要说明CMOS电路主要参数的特点。

(1)输出高电平VOH与输出低电平VOL。CMOS门电路VOH的理论值为电源电压VDD,VOH(min)=0.9VDD;VOL的理论值为0V,VOL(max)=0.01VDD。所以CMOS门电路的逻辑摆幅(即高低电平之差)较大,接近电源电压VDD值。

(2)阈值电压Vth。从CMOS非门电压传输特性曲线中看出,输出高低电平的过渡区很陡,阈值电压Vth约为VDD/2。

(3)抗干扰容限。CMOS非门的关门电平VOFF为0.45VDD,开门电平VON为0.55VDD。因此,其高、低电平噪声容限均达0.45VDD。其他CMOS门电路的噪声容限一般也大于0.3VDD,电源电压VDD越大,其抗干扰能力越强。

(4)传输延迟与功耗。CMOS电路的功耗很小,一般小于1 mW/门,但传输延迟较大,一般为几十ns/门,且与电源电压有关,电源电压越高,CMOS电路的传输延迟越小,功耗越大。前面提到74HC高速CMOS系列的工作速度己与TTL系列相当。

(5)扇出系数。因CMOS电路有极高的输入阻抗,故其扇出系数很大,一般额定扇出系数可达50。但必须指出的是,扇出系数是指驱动CMOS电路的个数,若就灌电流负载能力和拉电流负载能力而言,CMOS电路远远低于TTL电路。

CMOS逻辑门电路是在TTL电路问世之后 ,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件 。CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。此外,几乎所有的超大规模存储器件 ,以及PLD器件都采用CMOS艺制造,且费用较低。 早期生产的CMOS门电路为4000系列 ,随后发展为4000B系列。当前与TTL兼容的CMOS 器件如74HCT系列等可与TTL器件交换使用。

MOS管主要参数:1.开启电压VT

·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;·标准的N沟道MOS管,VT约为3~6V;·通过工艺上的改进,可以使MOS管的VT值降到2~3V。

2. 直流输入电阻RGS

·即在栅源极之间加的电压与栅极电流之比

·这一特性有时以流过栅极的栅流表示

·MOS管的RGS可以很容易地超过1010Ω。

3. 漏源击穿电压BVDS

·在VGS=0(增强型)的条件下 ,在增加漏源电压过程中使ID开始剧增时的VDS称为漏源击穿电压BVDS

·ID剧增的原因有下列两个方面:

(1)漏极附近耗尽层的雪崩击穿

(2)漏源极间的穿通击穿

·有些MOS管中,其沟道长度较短,不断增加VDS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的ID 。

4. 栅源击穿电压BVGS

·在增加栅源电压过程中,使栅极电流IG由零开始剧增时的VGS,称为栅源击穿电压BVGS。

5. 低频跨导gm

·在VDS为某一固定数值的条件下 ,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导

·gm反映了栅源电压对漏极电流的控制能力

·是表征MOS管放大能力的一个重要参数

·一般在十分之几至几mA/V的范围内 。

6. 导通电阻RON

·导通电阻RON说明了VDS对ID的影响 ,是漏极特性某一点切线的斜率的倒数

·在饱和区,ID几乎不随VDS改变,RON的数值很大 ,一般在几十千欧到几百千欧之间

·由于在数字电路中 ,MOS管导通时经常工作在VDS=0的状态下,所以这时的导通电阻RON可用原点的RON来近似

·对一般的MOS管而言,RON的数值在几百欧以内 。

7. 极间电容

·三个电极之间都存在着极间电容:栅源电容CGS 、栅漏电容CGD和漏源电容CDS

·CGS和CGD约为1~3pF

·CDS约在0.1~1pF之间。

8. 低频噪声系数NF

·噪声是由管子内部载流子运动的不规则性所引起的

·由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化

·噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)

·这个数值越小,代表管子所产生的噪声越小

·低频噪声系数是在低频范围内测出的噪声系数

·场效应管的噪声系数约为几个分贝,它比双极性三极管的要小 。

1.开启电压VT

·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;·标准的N沟道MOS管,VT约为3~6V;·通过工艺上的改进,可以使MOS管的VT值降到2~3V。

2. 直流输入电阻RGS

·即在栅源极之间加的电压与栅极电流之比

·这一特性有时以流过栅极的栅流表示

·MOS管的RGS可以很容易地超过1010Ω。

3. 漏源击穿电压BVDS

·在VGS=0(增强型)的条件下 ,在增加漏源电压过程中使ID开始剧增时的VDS称为漏源击穿电压BVDS

·ID剧增的原因有下列两个方面:

(1)漏极附近耗尽层的雪崩击穿

(2)漏源极间的穿通击穿

·有些MOS管中,其沟道长度较短,不断增加VDS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的ID 。

4. 栅源击穿电压BVGS

·在增加栅源电压过程中,使栅极电流IG由零开始剧增时的VGS,称为栅源击穿电压BVGS。

5. 低频跨导gm

·在VDS为某一固定数值的条件下 ,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导

·gm反映了栅源电压对漏极电流的控制能力

·是表征MOS管放大能力的一个重要参数

·一般在十分之几至几mA/V的范围内 。

6. 导通电阻RON

·导通电阻RON说明了VDS对ID的影响 ,是漏极特性某一点切线的斜率的倒数

·在饱和区,ID几乎不随VDS改变,RON的数值很大 ,一般在几十千欧到几百千欧之间

·由于在数字电路中 ,MOS管导通时经常工作在VDS=0的状态下,所以这时的导通电阻RON可用原点的RON来近似

·对一般的MOS管而言,RON的数值在几百欧以内 。

7. 极间电容

·三个电极之间都存在着极间电容:栅源电容CGS 、栅漏电容CGD和漏源电容CDS

·CGS和CGD约为1~3pF

·CDS约在0.1~1pF之间。

8. 低频噪声系数NF

·噪声是由管子内部载流子运动的不规则性所引起的

·由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化

·噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)

·这个数值越小,代表管子所产生的噪声越小

·低频噪声系数是在低频范围内测出的噪声系数

·场效应管的噪声系数约为几个分贝,它比双极性三极管的要小 。2100433B

CMOS是单词的首字母缩写,集成电路是一块微小的硅片,它包含有几百万个电子元件。术语IC隐含的含义是将多个单独的集成电路集成到一个电路中,产生一个十分紧凑的器件。在通常的术语中,集成电路通常称为芯片,而为计算机应用设计的IC称为计算机芯片。

虽然制造集成电路的方法有多种,但对于数字逻辑电路而言CMOS是主要的方法。桌面个人计算机、工作站、视频游戏以及其它成千上万的其它产品都依赖于CMOS集成电路来完成所需的功能。当我们注意到所有的个人计算机都使用专门的CMOS芯片,如众所周知的微处理器,来获得计算性能时, CMOS IC的重要性就不言而喻了。CMOS之所以流行的一些原因为:

·逻辑函数很容易用CMOS电路来实现。

·CMOS允许极高的逻辑集成密度。其含义就是逻辑电路可以做得非常小,可以制造在极小的面积上。

·用于制造硅片CMOS芯片的工艺已经是众所周知,并且CMOS芯片的制造和销售价格十分合理。

这些特征及其它特征都为CMOS成为制造IC的主要工艺提供了基础。

CMOS可以作为学习在电子网络中如何实现逻辑功能的工具。CMOS它允许我们用简单的概念和模型来构造逻辑电路。而理解这些概念只需要基本的电子学概念。

CMOS逻辑门电路的系列及主要参数:

1.CMOS逻辑门电路的系列

CMOS集成电路诞生于20世纪60年代末,经过制造工艺的不断改进,在应用的广度上已与TTL平分秋色,它的技术参数从总体上说,已经达到或接近TTL的水平,其中功耗、噪声容限、扇出系数等参数优于TTL。CMOS集成电路主要有以下几个系列。

(1)基本的CMOS——4000系列。

这是早期的CMOS集成逻辑门产品,工作电源电压范围为3~18V,由于具有功耗低、噪声容限大、扇出系数大等优点,已得到普遍使用。缺点是工作速度较低,平均传输延迟时间为几十ns,最高工作频率小于5MHz。

(2)高速的CMOS——HC(HCT)系列。

该系列电路主要从制造工艺上作了改进,使其大大提高了工作速度,平均传输延迟时间小于10ns,最高工作频率可达50MHz。HC系列的电源电压范围为2~6V。HCT系列的主要特点是与TTL器件电压兼容,它的电源电压范围为4.5~5.5V。它的输入电压参数为VIH(min)=2.0V;VIL(max)=0.8V,与TTL完全相同。另外,74HC/HCT系列与74LS系列的产品,只要最后3位数字相同,则两种器件的逻辑功能、外形尺寸,引脚排列顺序也完全相同,这样就为以CMOS产品代替TTL产品提供了方便。

(3)先进的CMOS——AC(ACT)系列

该系列的工作频率得到了进一步的提高,同时保持了CMOS超低功耗的特点。其中ACT系列与TTL器件电压兼容,电源电压范围为4.5~5.5V。AC系列的电源电压范围为1.5~5.5V。AC(ACT)系列的逻辑功能、引脚排列顺序等都与同型号的HC(HCT)系列完全相同。

2.CMOS逻辑门电路的主要参数

CMOS门电路主要参数的定义同TTL电路,下面主要说明CMOS电路主要参数的特点。

(1)输出高电平VOH与输出低电平VOL。CMOS门电路VOH的理论值为电源电压VDD,VOH(min)=0.9VDD;VOL的理论值为0V,VOL(max)=0.01VDD。所以CMOS门电路的逻辑摆幅(即高低电平之差)较大,接近电源电压VDD值。

(2)阈值电压Vth。从CMOS非门电压传输特性曲线中看出,输出高低电平的过渡区很陡,阈值电压Vth约为VDD/2。

(3)抗干扰容限。CMOS非门的关门电平VOFF为0.45VDD,开门电平VON为0.55VDD。因此,其高、低电平噪声容限均达0.45VDD。其他CMOS门电路的噪声容限一般也大于0.3VDD,电源电压VDD越大,其抗干扰能力越强。

(4)传输延迟与功耗。CMOS电路的功耗很小,一般小于1 mW/门,但传输延迟较大,一般为几十ns/门,且与电源电压有关,电源电压越高,CMOS电路的传输延迟越小,功耗越大。前面提到74HC高速CMOS系列的工作速度己与TTL系列相当。

(5)扇出系数。因CMOS电路有极高的输入阻抗,故其扇出系数很大,一般额定扇出系数可达50。但必须指出的是,扇出系数是指驱动CMOS电路的个数,若就灌电流负载能力和拉电流负载能力而言,CMOS电路远远低于TTL电路。

CMOS逻辑门电路是在TTL电路问世之后 ,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件 。CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。此外,几乎所有的超大规模存储器件 ,以及PLD器件都采用CMOS艺制造,且费用较低。 早期生产的CMOS门电路为4000系列 ,随后发展为4000B系列。当前与TTL兼容的CMOS 器件如74HCT系列等可与TTL器件交换使用。

这个是不能减小的,即使你电阻加的再大,因为二极管的特性是只要两端压差高于0.7就导通, 你可以把电阻跟5V当一个整体看,至于你第二个问题这很明显啊, 因为A才0.3V A肯定先通啊,A通了 后F点电压...

CMOS(Complementary Metal Oxide Semiconductor),互补金属氧化物半导体,电压控制的一种放大器件。是组成CMOS数字集成电路的基本单元。 发展历史 1963年,...

如果题目不限制使用的逻辑门类型,就很容易。Y=AB+AC+BC三个二输入端与门,输出接入一个三输入端或门。http://zhidao.baidu.com/question/489247413.html...

数字电路第5章时序逻辑电路

数字电路第5章时序逻辑电路

数字电路第5章时序逻辑电路

数字电路第5章时序逻辑电路

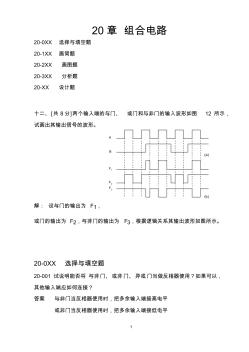

第20章习题2-门电路和组合逻辑电路

第20章习题2-门电路和组合逻辑电路

第20章习题2-门电路和组合逻辑电路

1 20章 组合电路 20-0XX 选择与填空题 20-1XX 画简题 20-2XX 画图题 20-3XX 分析题 20-XX 设计题 十二、 [共 8分]两个输入端的与门、 或门和与非门的输入波形如图 12 所示, 试画出其输出信号的波形。 解: 设与门的输出为 F1, 或门的输出为 F2,与非门的输出为 F3,根据逻辑关系其输出波形如图所示。 20-0XX 选择与填空题 20-001 试说明能否将 与非门、或非门、异或门当做反相器使用?如果可以, 其他输入端应如何连接? 答案 与非门当反相器使用时,把多余输入端接高电平 或非门当反相器使用时,把多余输入端接低电平 A B F1 F2 F3 (a) (b) 2 异或门当反相器使用时,把多余输入端接高电平 20-002、试比较 TTL 电路和 CMOS电路的优、缺点。 答案 COMS 电路抗干扰能力强, 速度快,静态损耗小,工作电压范围

CMOS逻辑电路缓冲器最基本线路构成的门电路存在着抗干扰性能差和不对称等缺点。为了克服这些缺点,可以在输出或输入端附加反相器作为缓冲级;也可以输出或输入端同时都加反相器作为缓冲级。这样组成的门电路称为带缓冲器的门电路。带缓冲输出的门电路输出端都是1个反相器,输出驱动能力仅由该输出级的管子特性决定,与各输入端所处逻辑状态无关。而不带缓冲器的门电路其输出驱动能力与输入状态有关。另一方面。带缓冲器的门电路的转移特性至少是由3级转移特性相乘的结果,因此转换区域窄,形状接近理想矩形,并且不随输入使用端数的情况而变化、加缓冲器的门电路,抗干扰性能提高10%电源电压。此外,带缓冲器的门电路还有输出波形对称、交流电压增益大、带宽窄、输入电容比较小等优点。不过,由于附加了缓冲级,也带来了一些缺点。例如传输延迟时间加大,因此,带缓冲器的门电路不适宜用在高速电路系统中。

在CPU的设计中,一般输出线的直流负载能力可以驱动一个TTL负载,而在连接中,CPU的一根地址线或数据线,可能连接多个存储器芯片,但存储器芯片都为MOS电路,主要是电容负载,直流负载远小于TTL负载。故小型系统中,CPU可与存储器直接相连,在大型系统中就需要加缓冲器。

CMOS逻辑电路缓冲器何程序或数据要为CPU所使用,必须先放到主存储器(内存)中,即CPU只与主存交换数据,所以主存的速度在很大程度上决定了系统的运行速度。程序在运行期间,在一个较短的时间间隔内,由程序产生的地址往往集中在存储器的一个很小范围的地址空间内。指令地址本来就是连续分布的,再加上循环程序段和子程序段要多次重复执行,因此对这些地址中的内容的访问就自然的具有时间集中分布的倾向。数据分布的集中倾向不如程序这么明显,但对数组的存储和访问以及工作单元的选择可以使存储器地址相对地集中。这种对局部范围的存储器地址频繁访问,而对此范围外的地址访问甚少的现象被称为程序访问的局部化(Locality of Reference)性质。由此性质可知,在这个局部范围内被访问的信息集合随时间的变化是很缓慢的,如果把在一段时间内一定地址范围被频繁访问的信息集合成批地从主存中读到一个能高速存取的小容量存储器中存放起来,供程序在这段时间内随时采用而减少或不再去访问速度较慢的主存,就可以加快程序的运行速度。这个介于CPU和主存之间的高速小容量存储器就称之为高速缓冲存储器,简称Cache。不难看出,程序访问的局部化性质是Cache得以实现的原理基础。同理,构造磁盘高速缓冲存储器(简称磁盘Cache),也将提高系统的整体运行速度。CPU一般设有一级缓存(L1 Cache)和二级缓存(L2 Cache)。一级缓存是由CPU制造商直接做在CPU内部的,其速度极快,但容量较小,一般只有十几K。PⅡ以前的PC一般都是将二级缓存做在主板上,并且可以人为升级,其容量从256KB到1MB不等,而PⅡ CPU则采用了全新的封装方式,把CPU内核与二级缓存一起封装在一只金属盒内,并且不可以升级。二级缓存一般比一级缓存大一个数量级以上,另外,在CPU中,已经出现了带有三级缓存的情况。Cache的基本操作有读和写,其衡量指标为命中率,即在有Cache高速缓冲存储器:

CMOS逻辑电路缓冲器上面介绍的基本都是常说的内存的方方面面,下面我们来认识一下高速缓冲存储器,即Cache。我们知道,任何程序或数据要为CPU所使用,必须先放到主存储器(内存)中,即CPU只与主存交换数据,所以主存的速度在很大程度上决定了系统的运行速度。程序在运行期间,在一个较短的时间间隔内,由程序产生的地址往往集中在存储器的一个很小范围的地址空间内。指令地址本来就是连续分布的,再加上循环程序段和子程序段要多次重复执行,因此对这些地址中的内容的访问就自然的具有时间集中分布的倾向。数据分布的集中倾向不如程序这么明显,但对数组的存储和访问以及工作单元的选择可以使存储器地址相对地集中。这种对局部范围的存储器地址频繁访问,而对此范围外的地址访问甚少的现象被称为程序访问的局部化(Locality of Reference)性质。由此性质可知,在这个局部范围内被访问的信息集合随时间的变化是很缓慢的,如果把在一段时间内一定地址范围被频繁访问的信息集合成批地从主的系统中,CPU访问数据时,在Cache中能直接找到的概率,它是Cache的一个重要指标,与Cache的大小、替换算法、程序特性等因素有关。增加Cache后,CPU访问主存的速度是可以预算的,64KB的Cache可以缓冲4MB的主存,且命中率都在90%以上。以主频为100MHz的CPU(时钟周期约为10ns)、20ns的Cache、70ns的RAM、命中率为90%计算,CPU访问主存的周期为:有Cache时,20×0.9 70×0.1=34ns;无Cache时,70×1=70ns。由此可见,加了Cache后,CPU访问主存的速度大大提高了,但有一点需注意,加Cache只是加快了CPU访问主存的速度,而CPU访问主存只是计算机整个操作的一部分,所以增加Cache对系统整体速度只能提高10~20%左右。

缓冲寄存器又称缓冲器,它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。由于缓冲器接在数据总线上,故必须具有三态输出功能。