INDF寄存器文献

嵌入式ARM9通过寄存器控制led灯

嵌入式ARM9通过寄存器控制led灯

嵌入式ARM9通过寄存器控制led灯

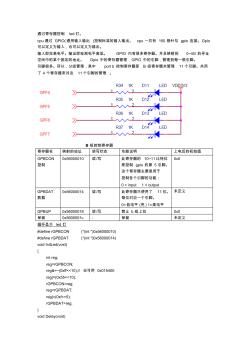

通过寄存器控制 led灯。 cpu通过 GPIO(通用输入输出 )控制标准的输入输出。 cpu 一共有 150 根针与 gpio 连接。Gpio 可以定义为输入,也可以定义为输出。 输入即拉高电平。输出即检测电平高低。 GPIO 内有很多寄存器。并且映射到 0~4G 的寻址 空间中的某个固定的地址。 Gpio 中的寄存器管理 GPIO 中的引脚,管理到每一根引脚。 引脚很多。所以,分组管理,其中 port b 控制寄存器即 B 组寄存器共管理 11个引脚。共用 了 4 个寄存器来对这 11个引脚的管理 。 B 组控制寄存器 寄存器名 映射的地址 读写状态 功能说明 上电后的初始值 GPBCON 控制 0x56000010 读 /写 此寄存器的 10~11比特位 即控制 gpio 的第 5 引脚。 这个寄存器主要是用于 控制各个引脚的功能: 0 = input 1 = output 0x0

基于可逆触发器的可逆移位寄存器设计方法

基于可逆触发器的可逆移位寄存器设计方法

基于可逆触发器的可逆移位寄存器设计方法

为了进一步提高可逆时序逻辑电路设计方法的通用性和改善可逆电路性能指标,以可逆主从D触发器为基本单元,通过将时钟信号及垃圾位信号级联再利用,提出了一种可逆串行移位寄存器优化设计方案。在此基础上,通过目标函数构造及变换构建带有移位控制的单元模块,设计了满足串行输入串/并行输出功能的n位可逆双向移位寄存器。设计结果表明,采用方法所设计的可逆移位寄存器具有较优的性能指标,且对于双向移位寄存器综合具有较好的通用性。