差分电路差分放大器影响CMRR的因素文献

尺寸及版图设计对集成电路差分放大器性能的影响

尺寸及版图设计对集成电路差分放大器性能的影响

尺寸及版图设计对集成电路差分放大器性能的影响

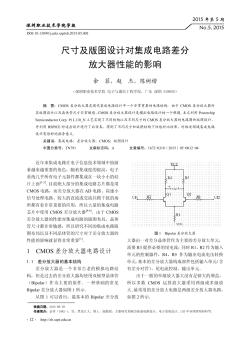

CMOS差分放大器是现代集成电路设计中一个非常重要的电路结构.由于CMOS差分放大器对其版图设计以及晶体管尺寸非常敏感,CMOS差分放大器设计是模拟电路设计的一个难题.本文利用PowerchipSemiconductorCorp的L110-N工艺实现了不同结构以及不同尺寸的CMOS差分放大器的电路图和版图设计,并利用HSPICE对这些设计进行了后仿真,得到了不同尺寸和版图结构下性能对比结果,对相关领域集成电路设计有很好的指导意义.

尺寸及版图设计对集成电路差分放大器性能的影响

尺寸及版图设计对集成电路差分放大器性能的影响

尺寸及版图设计对集成电路差分放大器性能的影响

CMOS差分放大器是现代集成电路设计中一个非常重要的电路结构.由于CMOS差分放大器对其版图设计以及晶体管尺寸非常敏感,CMOS差分放大器设计是模拟电路设计的一个难题.本文利用Powerchip Semiconductor Corp的L110_N工艺实现了不同结构以及不同尺寸的CMOS差分放大器的电路图和版图设计,并利用HSPICE对这些设计进行了后仿真,得到了不同尺寸和版图结构下性能对比结果,对相关领域集成电路设计有很好的指导意义.