Lvds文献

SN65LVDS2DBVRG4中文资料

SN65LVDS2DBVRG4中文资料

SN65LVDS2DBVRG4中文资料

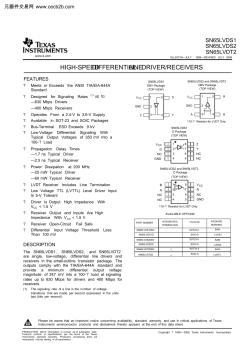

www.ti.com FEATURES DESCRIPTION 3 2 4 5 (TOP VIEW) 1V CC GND Z D Y SN65LVDS1 DBV Package 3 2 4 5 (TOP VIEW) 1V CC GND A R B SN65LVDS2 and SN65LVDT2 DBV Package VCC D NC GND Z Y NC NC SN65LVDS1 D Package (TOP VIEW) 1 2 3 4 8 7 6 5 B A NC NC VCC R NC GND SN65LVDS2 and SN65LVDT2 D Package (TOP VIEW) 1 2 3 4 8 7 6 5 PART NUMBER INTEGRATED TERMINATION PACKAGE SOT23-5 PACKAGE MARKING SN65LVDS1DBV SN65LV

总线LVDS驱动器电路设计

总线LVDS驱动器电路设计

总线LVDS驱动器电路设计

提出了一种用于多点数据传输的BLVDS(Bus low voltage differential signal)驱动器电路设计。设计中将电压模式驱动器电路和双电流源模式驱动器电路相结合实现多点数据传输,既充分利用了LVDS技术高速、低功耗和低噪声的优点,又解决了传统的LVDS驱动器电路只能用于点对点应用,不能用于总线数据传输的问题。仿真结果表明,该BLVDS驱动器电路的传输速率可达100Mbps,电气性能指标符合TIA/EIA-899协议标准的要求。