由于连接到I2C 总线的器件有不同种类的工艺(CMOS、NMOS、PMOS、双极性),逻辑0(低)和逻辑1(高)的电平不是固定的,它由电源VCC的相关电平决定,每传输一个数据位就产生一个时钟脉冲。

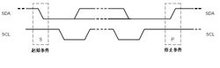

在传输数据的时候,SDA线必须在时钟的高电平周期保持稳定,SDA的高或低电平状态只 有在SCL 线的时钟信号是低电平时才能改变 。

有在SCL 线的时钟信号是低电平时才能改变 。

SCL 线是高电平时,SDA 线从高电平向低电平切换,这个情况表示起始条件;

SCL 线是高电平时,SDA 线由低电平向高电平切换,这个情况表示停止条件。

起始和停止条件一般由主机产生,总线在起始条件后被认为处于忙的状态 ,在停止条件的某段时间后总线被认为再次处于空闲状态。

,在停止条件的某段时间后总线被认为再次处于空闲状态。

如果产生重复起始条件而不产生停止条件,总线会一直处于忙的状态,此时的起始条件(S)和重复起始条件(Sr) 在功能上是一样的。