FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成。因此FPGA实现除法运算并不是一个“/”号可以解决的。

好在此类基本运算均有免费的IP核使用,本人使用的VIVADO 2016.4开发环境提供的divider gen IP核均采用AXI总线接口,已经不再支持naTIve接口。故做除法运算的重点从设计算法电路转变成了调用AXI总线IP核以及HDL中有符号数的表示问题,极大降低了开发难度。以下就上述两个方面进行探讨。

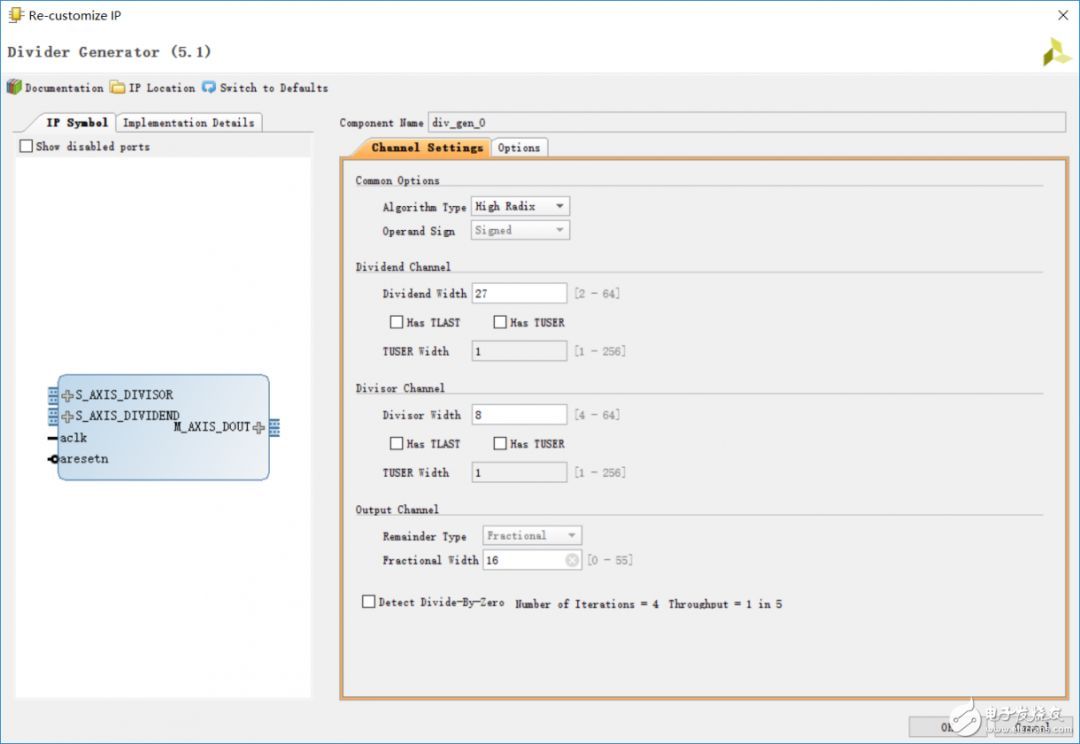

VerilogHDL中默认数据类型为无符号数,因此需要数学运算的场合必须要用“signed”声明,如:reg signed [8-1:0] signal_a;wire signed [32-1:0] signal_b;需要注意一点,FPGA将所有有符号数视为二进制补码形式,运算的结果同样为补码。再来看看除法器IP核配置界面。

总共就两页,非常简单。需要重点关注的有三个地方:1 算法实现结构(algorithm type)2 被除数与除数的位宽 3 第二页flow control模式。现来一一说明:

就算法结构来说官方文档pg151 LogiCORE IP Product Guide中说得很详细:LUTMult结构操作数最好不要高于12bit,且充分利用DSP slice和BRAM以降低对FPGA 逻辑资源的消耗。Radix-2操作数不要超过16bit,且利用资源与LUTMulTI相反,大量使用register和LUT从而将DSP slice和BRAM资源节省出来用在别的地方。最后一个High Radix结构支持超过16bit的大位宽操作数,利用DSPslice等专用硬件资源。根据自己的需求选择即可。

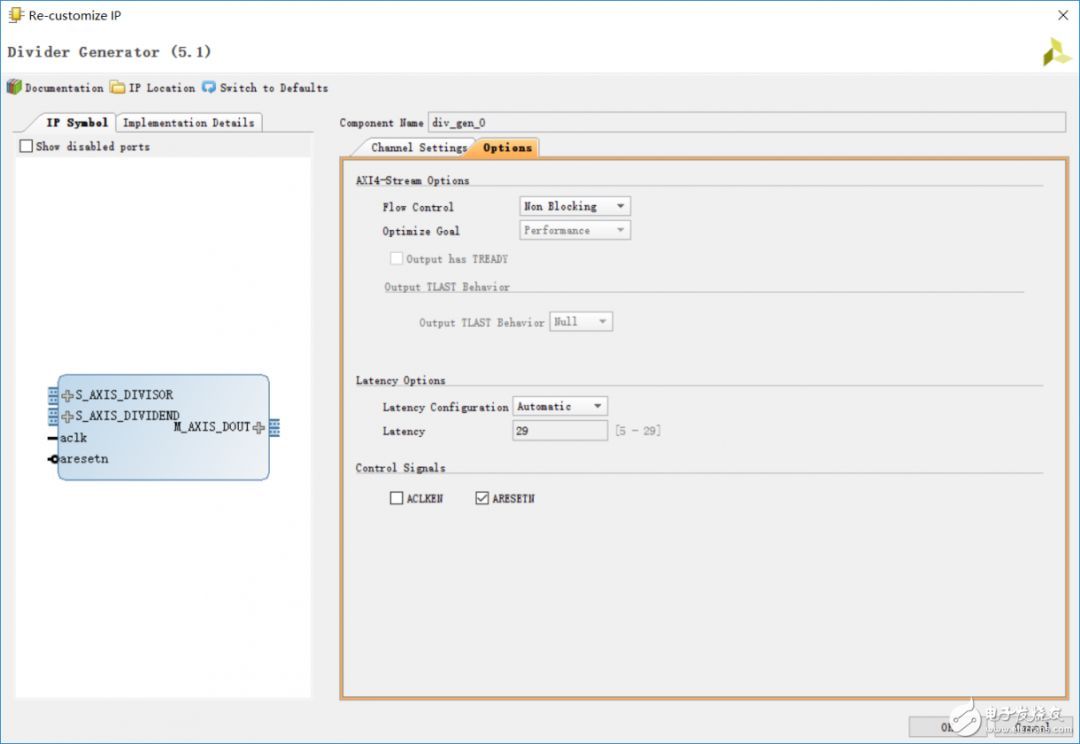

位宽问题没什么好说的,需要特别注意保留位宽满足计算范围,也就是运算之前的“补码符号位扩展”。至于flow control 模式与接口和AXI总线有关。

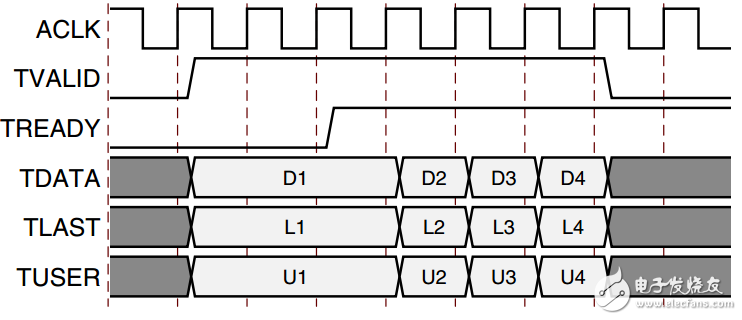

接口划分得十分清晰,被除数 除数和商通道以及必要的时钟和复位逻辑接口。每个AXI总线通道总是包括tdata tuser tlast 和握手信号tvalid tready,其中tuser为附加信息,tlast表示流模式下最后一个数据,相当于数据包中的包尾处。数据传输仅在tvalid和tready同时拉高时有效并更新。

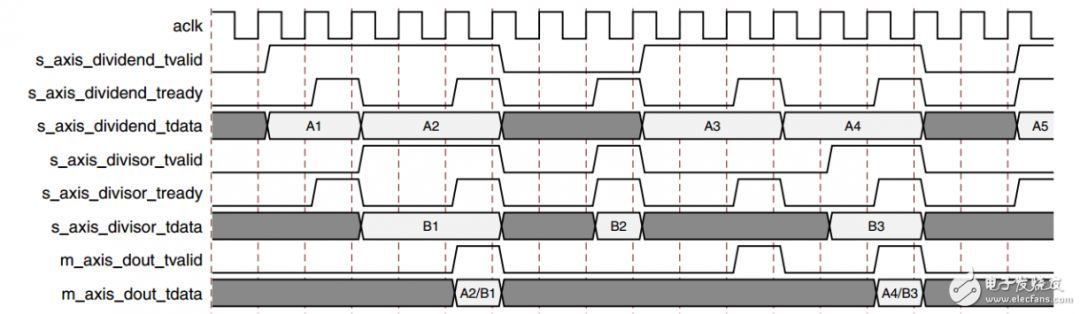

而Non Blocking Mode在除法运算时较常用,一句话概括:IP核接口不带有FIFO缓存,输出通道数据必须被下游模块实时处理。上图就明白了:

这一模式实际上是对AXI总线的简化,很多场合下并不完全需要AXI总线强大的流控功能,特别是在AXI总线模块的上下游均为可进行实时处理的FPGA逻辑电路的情况下。AXI总线的另一个特点就是data packing,需要将不是8bit倍数位宽的数据高位填充从而确保数据最小单位是1byte,具体填充方式有所不同。很容易想到,这样的data packing 功能对SOC中PL与PS部分的交互是十分友好的。

总体来说,在FPGA中做基本的数学运算没什么难度,即使是指数 对数 开根号之类的复杂运算也有浮点IP Core的支持。

免责声明:本文系网络转载,版权归原作者所有。如涉及作品版权问题,请与我们联系,我们将根据您提供的版权证明材料确认版权并支付稿酬或者删除内容。