Barry Olney

In-Circuit Design Pty Ltd(iCD) 董事总经理

AC/DC是世界顶级摇滚乐队之一。但在本月的专栏中,所要探讨的AC/DC是指高速串行链路的交流耦合。

图1:AC/DC在早期演出时激情四射(来源:Kat Benzova)

SERDES串行链路用于通过差分信号实现高速高带宽数据传输,并最大限度地减少I / O引脚和互连的数量。尽管这可以使PCB设计师不必大量并行布线,但实施高速串行链路仍具有挑战。物理布线中沿传输路径的任何小的不连续性都会明显降低信号的质量,包括波幅损失、上升时间减少和抖动增加。因此,人们必须能够在高速通道中识别这些不连续性,并减轻其影响,提高信号传输性能。

通常将电容与2个差分信号线串联,以消除IC器件或不同工艺之间的共模压差。“交流耦合电容”或“隔直流电容”基本上是指同一件事。与信号路径串联放置的任何电容都倾向于通过信号的高频交流部分,同时阻隔低频直流部分。由于这些电容对发射端和接收端起耦合作用,所以我更喜欢使用术语“交流耦合”。

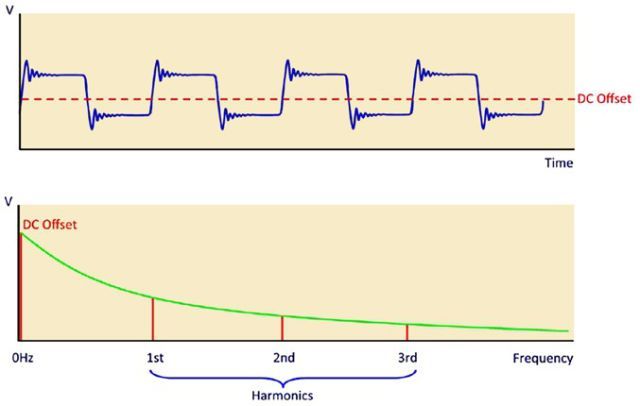

图2:转换到频域的信号交流分量和直流分量

图2的上图中,信号在直流偏移附近波动。对由交流分量和直流分量组成的信号进行傅立叶变换后,直流分量的频率为0 Hz,交流信号则为其相关谐波频率(下图)。

交流耦合是有用的,因为信号的直流分量作为电压偏移,消除它可以提高信号的分辨率,并可以使不同工艺在没有电平移位器的情况下能够进行通信。电平移位器IC则可以提供在不同电压下运行的元器件之间的接口。然而,电平移位器会引入延迟变化(偏移),增加功耗,并且不适用于低电源电压。需要交流耦合来保持接收端的正确直流偏置。如果发送端具有0 V直流偏压并且与接收端具有相同的工艺,则不必采取交流耦合措施。

交流耦合电容最重要的参数是与基板有关的相对几何尺寸。电容与高速布线串联,因此电容本体成为传输线的一部分。电容的等效串联电感(ESL),对于旁路和去耦应用来说是关键的,对于交流耦合应用却是可以忽略不计的,因为传输线自身就具有固有电感。而电容器区域中的外部电介质叠层的厚度、布线宽度、焊盘尺寸、焊料厚度和覆盖层厚度都会相互影响。

在匹配良好的互连中, AC耦合电容的放置位置并不重要。问题的关键在于电容器瞬态特性设计有多好、反射率有多低,以及是否放置在其他信道不连续处附近。最好是远离其他不连续处。

交流耦合消除了共模电平,并允许接收端设置自己的偏置点。这对于机架到机架系统特别有用,这种系统无法很好地控制共模。交流耦合还具有以下优点:

□ VTT参考和GND参考系统可一起工作

□一个SERDES通道可涵盖多个标准

□较新的(受限供应)器件可与传统器件一起使用

□热插拔和防止外部短路的能力

但是,交流耦合电容是高速串行通道中阻抗不连续的常见原因。通常,使用窄走线宽度和密走线间距来构建100 Ω差分传输线对。然而,由于这些窄的走线对被布线到电容器的表面贴装焊盘,当铜与电容焊盘连接时突然变宽,导致突变的阻抗不连续。这种不连续性的影响表现为过大电容量,因为电容的表面贴装焊盘,就如同底部参考平面的平行板。

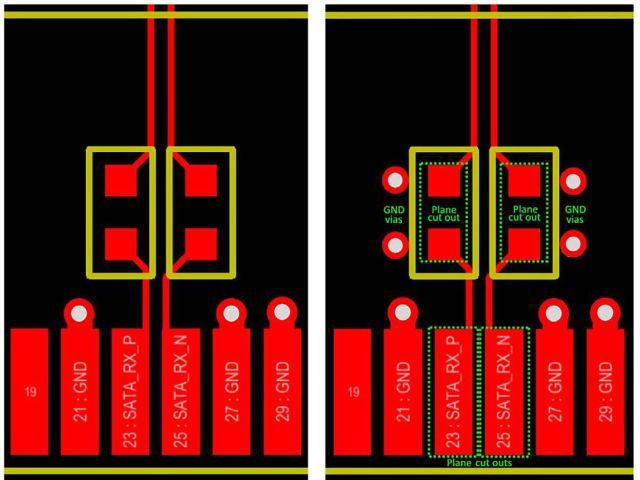

为了消除与表面安装焊盘有关的多余寄生电容,应该去除元件正下方的参考平面的一部分,让穿过电容器的信号参考更低的平面(更远的距离),并减小寄生电容,从而使阻抗不匹配最小化。如果线路中存在表面贴装连接器,这一原则也应该适用(图3)。

图3:带有平面切口和GND过孔(右侧)的交流耦合电容(左侧)

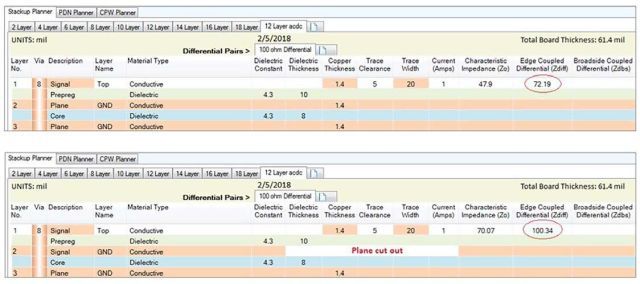

在左侧,有2个参考第二层平面的电容器。而右侧的图片显示了包含平面切口的优化结构,然后这些焊盘参考第三层平面,增加了阻抗。电路板叠层和走线几何形状(图4)的设计可提供100 Ω差分信号。所有的布线和平面层都是1盎司铜。表面贴装焊盘的宽度设置为20 mil,为了和0402电容的宽度匹配。并且,切口的长度等于2个表面贴装焊盘的端到端距离。iCD Stackup Planner工具可用于预估信号层到第三层的较低平面的阻抗,第三层取代了第二层。这样可将阻抗从72 Ω增加到100 Ω。

图3中的AC耦合电容附近的4个接地导通孔和连接器焊盘上的2个接地导通孔,对于为直流电流提供到较低GND平面的返回路径是必不可少的。正确放置通孔,将起到使串扰最小化的作用,并减小由于信号偏移而产生的共模电压。接收端附近的共模转换会受到一些其他信号源串扰峰值的影响。

图4:去除电容下方的平面后,阻抗达到了100 Ω(来源:iCD Stackup Planner)

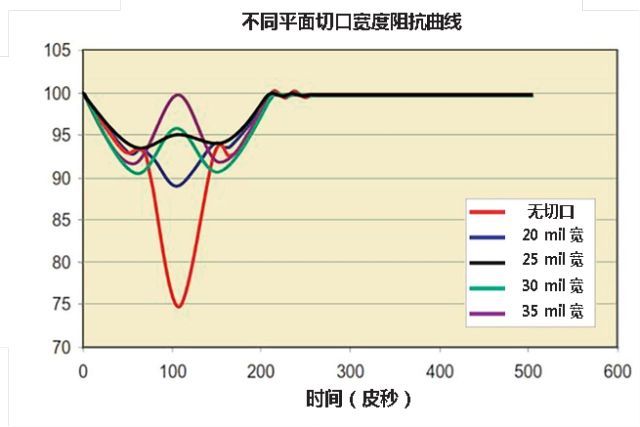

图5显示了Ansoft HFSS模拟的TDR阻抗曲线。红线是在AC耦合电容的表面贴切装焊盘下没有平面切口时的高速差分走线的阻抗曲线,其他则是切口设置为不同宽度时的阻抗曲线。

仿真结果表明平面切口的宽度在最小化阻抗不匹配中起着重要作用。没有平面切口时,电容器焊盘处的阻抗低于75 Ω,但是,这时需要增加到100 Ω以避免反射;当切口的宽度为25密耳时,可以实现最小的阻抗不匹配,因而25 mil的切口宽度是最佳结构。对于大多数应用, AC耦合电容采用0402封装,电容值为100 nF就足够了。

图5:不同平面切口宽度阻抗曲线的TDR仿真(来源:Altera)

如果您没有可用的仿真工具,这是一个可以遵循的基本指导原则。如果较低的平面是电源平面或者没有较低平面,则可以在电容器下方区域中注入接地填充物,并在每个电容焊盘附近打4个GND导通孔。

系统失败的原因多种多样,并且与多个元器件反射的相互作用有关。优化是免费的,裕度工程产生的是非经常性费用,因此在制造成本方面为零。一旦完成,裕度总是在那里,并且无需成本。

关键点

■ 沿传输路径的物理几何形状的不连续性会导致信号幅度损失、上升时间减少和抖动增加,从而降低信号质量;

■ 电容器通常与两个差分信号走线串联,以消除共模压差;

■交流耦合很有用,因为信号的直流分量可以用作电压偏移,而去除它可以提高信号的分辨率,并允许具有不同工艺的发送端/接收端进行通信;

■交流耦合电容最重要的参数是其环境的相对几何尺寸;

■沿传输路径放置AC耦合电容的位置并不重要;

■电容瞬态特性非常关键:反射率有多低,以及是否放置在其他通道不连续点附近;

■交流耦合消除了共模电平,并允许接收端设置自己的偏置点;

■ 为了消除与表面贴装焊盘有关的多余寄生电容,可以去除元器件正下方的参考平面的一部分;

■放置于交流耦合电容附近的接地通孔是必要的,它们可为直流电流提供到较低GND平面的返回路径;

■当电容器下方的切口宽度为25 mil时,可实现最小的阻抗不匹配,因而是最佳结构;

■ 对于大多数应用, AC耦合电容采用100 nF的0402封装电容就够了。

In-Circuit Design是一家专门从事板级模拟的PCB设计服务机构。该公司开发了iCD Design Integrity软件,包括iCD Stackup、PDN and CPW Planner。该软件可以从 www.icd.com.au下载。