精品文献

74ls138译码器

EDA:4-16译码器电路的设计

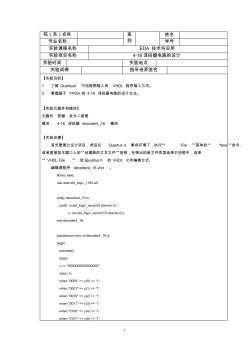

1 院(系)名称 班 别 姓名 专业名称 学号 实验课程名称 EDA 技术与应用 实验项目名称 4-16译码器电路的设计 实验时间 实验地点 实验成绩 指导老师签名 【实验目的】 1. 了解 QuartusII 中电路图输入和 VHDL 程序输入方式。 2. 掌握基于 FPGA 的 4-16 译码器电路的设计方法。 【实验元器件和模块】 元器件:按键、发光二极管 模块: 4-16 译码器 decoder4_16 模块 【实验步骤】 首先要建立设计项目,然后在 Quartus II 集成环境下,执行“ File ”菜单的“ New”命令, 或者直接按主窗口上的“创建新的文本文件”按钮,在弹出的新文件类型选择对话框中,选择 “ VHDL File ”,进入Quartus II 的 VHDL 文本编辑方式。 编辑源程序 decoder4_16.vhd 。 library ieee; use

8位计数译码器的设计

【例 4.15】用模块例化方式设计 8位计数译码器电路系统。 在 8 位计数译码系统电路设计中, 需要事先设计一个 4 位二进制加法计数器 cnt4e 模块 和一个七段数码显示器的译码器 dec7s模块,然后用模块例化方式将这两种模块组成计数译 码系统电路。 1. 4位二进制加法计数器 cnt4e 的设计 cnt4e 的元件符号如图 4.11 所示, clk 是时钟输入端; clr 是复位控制输入端,当 clr=1 时计数器被复位,输出 q[3..0]=0000;ena 是使能控制输入端,当 ena=1 时,计数器才能工 作; cout 是进位输出端,当输出 q[3..0]=1111 时, cout=1。 Cnt4e 的 Verilog HDL 源程序 cnt4e.v 如下: module cnt4e (clk,clr,ena,cout,q); input clk,clr,ena; o