选择特殊符号

选择搜索类型

请输入搜索

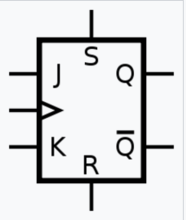

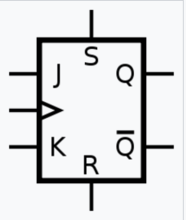

JK触发器 逻辑简图如右图所示

JK触发器和触发器中最基本的RS触发器结构相似,其区别在于,RS触发器不允许R与S同时为1,而JK触发器允许J与K同时为1。当J与K同时变为1的同时,输出的值状态会反转。也就是说,原来是0的话,变成1;原来是1的话,变成0。 对应表如下:

| JK触发器运算 | |||||

|---|---|---|---|---|---|

| J | K | 动作 | Q | Qnext | 动作 |

| 0 | 0 | 保持 | X | X | 不变 |

| 0 | 1 | 重置 | X | 0 | 重置 |

| 1 | 0 | 设置 | X | 1 | 设置 |

| 1 | 1 | 反转 | 1(0) | 0(1) | 反转 |

JK触发器的时序图

脉冲工作特性如右图所示

该触发器无一次变化现象,输入信号可在CP 触发沿由1变0时刻前加入。由图7.6.1可知,该电路要求J、K信号先于CP 信号触发沿传输到G3、G4的输出端,为此它们的加入时间至少应比CP 的触发沿提前一级与非门的延迟时间。这段时间称为建立时间test。

输入信号在负跳变触发沿来到后就不必保持,原因在于即使原来的J、K信号变化,还要经一级与非门的延迟才能传输到G3和G4的输出端,在此之前,触发器已由G12、G13、G22、G23的输出状态和触发器原先的状态决定翻转。所以这种触发器要求输入信号的维持时间极短,从而具有很高的抗干扰能力,且因缩短tCPH 可提高工作速度。

从负跳变触发沿到触发器输出状态稳定,也需要一定的延迟时间tCPL。显然,该延迟时间应大于两级与或非门的延迟时间。即tCPL大于2.8tpd。

综上所述,对边沿JK 触发器归纳为以下几点:

1.边沿JK 触发器具有置位、复位、保持(记忆)和计数功能; 2.边沿JK 触发器属于脉冲触发方式,触发翻转只在时钟脉冲的负跳变沿发生; 3.由于接收输入信号的工作在CP下降沿前完成,在下降沿触发翻转,在下降沿后触发器被封锁,所以不存在一次变化的现象,抗干扰性能好,工作速度快。

电路结构

主从JK 触发器是在主从RS触发器的基础上组成的,如图7.5.1所示。 在主从RS触发器的R端和S端分别增加一个两输入端的与门G11和G10,将Q端和输入端经与门输出为原S端,输入端称为J端,将Q端与输入端经与门输出为原R端,输入端称为K端。

工作原理

由上面的电路可得到S=JQ,R=KQ。代入主从RS触发器的特征方程得到:

当

J=1,K=0时,Qn+1=1;

J=0,K=1时,Qn+1=0;

J=K=0时,Qn+1=Qn;

J=K=1时,Qn+1=~Qn;

由以上分析,主从JK 触发器没有约束条件。在J=K=1时,每输入一个时钟脉冲,触发器翻转一次。触发器的这种工作状态称为计数状态,由触发器翻转的次数可以计算出输入时钟脉冲的个数。

工作特性

建立时间:是指输入信号应先于CP信号到达的时间,用tset表示。由图7.5.5可知,J、K信号只要不迟于CP信号到达即可,因此有tset=0。保持时间:为保证触发器可靠翻转,输入信号需要保持一定的时间。保持时间用tH表示。如果要求 CP=1期间J、K的状态保持不变,而CP=1的时间为tWH,则应满足:tH≥tWH。

传输延迟时间:若将从CP下降沿开始到输出端新状态稳定地建立起来的这段时间定义为传输时间,则有:tPLH=3tpd tPHL=4tpd 最高时钟频率:因为主从触发器都是由 两个同步RS 触发器组成的,所以由同步RS触发器的动态特性可知 ,为保证主触发器的可靠翻转,CP高电平的持续时间tWH应大于3tpd。同理,为保证从触发器能可靠地翻转, CP低电平的持续时间tWL也应大于3tpd。因此,时钟信号的最小周期为:Tc(min)≥6tpd 最高时钟频率fc(max)≤1/6tpd。

如果把图7.5.5的J、K触发器接成T触发器使用(即将J和K相连后接至高电平),则最高时钟频率还要低一些。因为从CP的下降沿开始到输出端的新状态稳定建立所需要的时间为tPHL≥4tpd,如果CP信号的占空比为50%,那么CP信号的最高频率只能达到fc(max)=1/2tPHL=1/8tpd。

若 Reset=0时:

J=1,K=0时,Qn+1=1;

J=0,K=1时,Qn+1=0;

J=K=0时,Qn+1=Qn;

J=K=1时,Qn+1=Qn; 若 Reset=1时:

不论J、K与Qn的值,Qn+1=0。

集成JK触发器的产品较多,以下介绍一种比较典型的高速CMOS双JK触发器HC76。该触发器内含两个相同的JK触发器,它们都带有预置和清零输入,属于负跳沿触发的边沿触发器,其逻辑符号和引脚分布如下图7.5.6 所示。其功能表如表7.5.1所示。如果在一片集成器件中有多个触发器,通常在符号前面(或后面)加上数字,以表示不同触发器的输入、输出信号,比如C1与1J、1K同属一个触发器。

综上所述

对主从JK 触发器归纳为以下几点:

1.主从JK触发器具有置位、复位、保持(记忆)和计数功能;

2.主从JK触发器属于脉冲触发方式,触发翻转只在时钟脉冲的负跳变沿发生;

3.不存在约束条件,但存在一次变化现象。4.产生一次变化的原因是因为在CP=1期间,主触发器一直在接收数据,但主触发器在某些条件下(Q=0,CP=1期间J端出现正跳沿干扰或Q=1,CP=1期间K端出现正跳沿干扰),不能完全随输入信号的变化而发生相应的变化,以至影响从触发器 状态与输入信号的不对应。

两个PNP三极管(上拉管)并联构成二输入与非门电路,三个PNP三极管并联则构成三输入与非门电路。

每个按键按下时提供高电平,松开时提供低电平。CLK按下时主触发器工作,松开时从触发器工作。

D触发器的状态方程是:Q*=D;jk触发器的状态方程是:Q*=JQ'+K'Q。让两式相等可得:D=JQ'+K'Q。用门电路实现上述函数即可转换成为jk触发器。你看下图就...

[编辑本段]边沿JK 触发器: 电路结构: 采用与或非电路结构,属于下降沿触发的边沿JK触发器,如图7.6.1所示。 工作原理 1.CP=0时,触发器处于一个稳态。 CP为0时,G3...

电子工程科-同步JK触发器的原理与特点

电子工程科-同步JK触发器的原理与特点

电子工程科-同步JK触发器的原理与特点

电子工程科-同步JK触发器的原理与特点

具有抗差分能量攻击性能的JK触发器设计

具有抗差分能量攻击性能的JK触发器设计

具有抗差分能量攻击性能的JK触发器设计

通过对传统触发器结构和旁道攻击密码系统原理的研究,提出一种具有抗差分能量攻击性能的JK触发器设计方案。首先,根据双轨预充逻辑电路交替处于预充阶段与求值阶段的特点,结合触发器的特征方程,推导出具有抗差分能量攻击性能的JK触发器的状态方程;然后,根据场效应管宽长比对数据传输速率的影响,采用灵敏放大型逻辑,得到相应的触发器电路结构。HSPICE模拟验证表明,所设计电路具有正确的逻辑功能。与传统JK触发器比较,该结构具有显著的抗差分能量攻击性能。

在电子电路中,有许多触发器采用下降沿触发方式,例如主从RS触发器(如下图)、下降沿JK边沿触发器等(详见JK触发器) 。

数字电路中要实现各部分协同工作,需要有统一的时钟脉冲来控制动作,简称为时钟CP,凡是有时钟信号控制的触发器均称为时钟触发器。时钟触发器又可分为同步触发器、主从触发器、边沿触发器。

时钟触发器按逻辑功能分为5种:时钟jk触发器、rs触发器、d触发器、t触发器、t'触发器。

在数字电路中

各类触发器相互转换

一般有二个步骤

①列真值表,把要转换的触发器作为Vi,把被转换的作为Vo。

②找出输出为1的信号中的逻辑表达式,并化简。

例如:

由JK触发器T触发器

例 T→JK

②找出输出为1的信号中的逻辑表达式,并化简

例 T→JK

根据真值表找出T为1的变量表达式并化简

T=|JKQn+|k|Qn Qn+1 +JK|QnQn+1 +JKQn|Qn+1

=KQn+JQn

画出逻辑电路图为: 可得JK触发器