封装技术

所谓"封装技术"是一种将集成电路用绝缘的塑料或陶瓷材料打包的技术。以CPU为例,实际看到的体积和外观并不是真正的CPU内核的大小和面貌,而是CPU内核等元件经过封装后的产品。封装技术封装对于芯片来说是必须的,也是至关重要的。因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。另一方面,封装后的芯片也更便于安装和运输。由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的PCB(印制电路板)的设计和制造,因此它是至关重要的。

-

选择特殊符号

选择搜索类型

请输入搜索

所谓"封装技术"是一种将集成电路用绝缘的塑料或陶瓷材料打包的技术。以CPU为例,实际看到的体积和外观并不是真正的CPU内核的大小和面貌,而是CPU内核等元件经过封装后的产品。封装技术封装对于芯片来说是必须的,也是至关重要的。因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。另一方面,封装后的芯片也更便于安装和运输。由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的PCB(印制电路板)的设计和制造,因此它是至关重要的。

从DIP封到BGA封装

芯片的封装技术种类实在是多种多样,诸如DIP,PQFP,TSOP,TSSOP,PGA,BGA,QFP,TQFP,QSOP,SOIC,SOJ,PLCC,WAFERS......一系列名称看上去都十分繁杂,其实,只要弄清芯片封装发展的历程也就不难理解了。芯片的封装技术已经历经好几代的变迁,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越接近,适用频率越来越高,耐温性能越来越好,以及引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等,都是看得见的变化。20世纪70年代时,芯片封装流行的还是双列直插封装,简称DIP(Dual ln-line Package)。DIP封装在当时具有适合PCB(印刷电路板)的穿孔安装,具有比TO型封装易于对PCB布线以及操作较为方便等一些特点,其封装的结构形式也很多,包括多层陶瓷双列直插式DIP,单层陶瓷双列直插式DIP,引线框架式DIP等等。但是衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。比如一颗采用40根I / O引脚塑料双列直插式封装(PDIP)的芯片为例,其芯片面积/封装面积=(3 x3)/(15.24 x 50)=1:86,离l相差很远。不难看出,这种封装尺寸远比芯片大不少,说明封装效率很低,占去了很多有效安装面积。

到了80年代出现的内存第二代封装技术以TSOP为代表,它很快为业界所普遍采用,到目前为止还保持着内存封装的主流地位。TSOP是英文Thin Small Outline Package的缩写,意即薄型小尺寸封装。TSOP内存封装技术的一个典型特征就是在封装芯片的周围做出引脚,如SDRAM内存的集成电路两侧都有引脚,SGRAM内存的集成电路四面都有引脚。TSOP适合用SMT技术(表面安装技术)在PCB(印制电路板)上安装布线。TSOP封装外形尺寸时,寄生参数(电流大幅度变化时,引起输出电压扰动) 减小,适合高频应用,操作比较方便,可靠性也比较高。改进的TSOP技术目前广泛应用于SDRAM内存的制造上,不少知名内存制造商如三星、现代、Kingston等目前都在采用这项技术进行内存封装。

20世纪90年代随着集成技术的进步、设备的改进和深亚微米技术的使用,LSI、VLSI、ULSI相继出现,芯片集成度不断提高,I / O引脚数急剧增加,功耗也随之增大,对集成电路封装的要求也更加严格。为满足发展的需要,在原有封装方式的基础上,又增添了新的方式一一球栅阵列封装,简称BGA(Ball Grid Array Package)。BGA封装技术已经在笔记本电脑的内存、主板芯片组等大规模集成电路的封装领域得到了广泛的应用。比如我们所熟知的Intel BX、VIA MVP3芯片组以及SODIMM等都是采用这一封装技术的产品。

BGA 封装技术有这样一些特点:I / O引脚数虽然增多,但引脚间距并不小,从而提高了组装成品率;虽然它的功耗增加,但BGA能用可控塌陷芯片法焊接,从而可以改善它的电热性能;厚度和重量都较以前的封装技术有所减少;寄生参数减小,信号传输延迟小,使用频率大大提高;组装可用共面焊接,可靠性高。不过BGA封装仍然存在着占用基板面积较大的问题。

随着以CPU为主的计算机系统性能的总体大幅度提升趋势,人们对于内存的品质和性能要求也日趋苛刻。为此,人们要求内存封装更加紧致,以适应大容量的内存芯片,同时也要求内存封装的散热性能更好,以适应越来越快的核心频率。毫无疑问的是,进展不太大的TSOP等内存封装技术也越来越不适用于高频、高速的新一代内存的封装需求,新的内存封装技术也应运而生了。采用BGA新技术封装的内存,可以使所有计算机中的DRAM内存在体积不变的情况下内存容量提高两到三倍,BGA与TSOP相比,具有更小的体积,更好的散热性能和电性能。BGA封装技术使每平方英寸的存储量有了很大提升,采用BGA封装技术的内存产品在相同容量下,体积只有TSOP封装的三分之一;另外,与传统TSOP封装方式相比,BGA封装方式有更加快速和有效的散热途径。

封装(Package)对于芯片来说是必须的,也是至关重要的。封装也可以说是指安装半导体集成电路芯片用的外壳,它不仅起着保护芯片和增强导热性能的作用,而且还是沟通芯片内部世界与外部电路的桥梁和规格通用功能的作用。封装的主要作用有:

(1)物理保护。因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降,保护芯片表面以及连接引线等,使相当柔嫩的芯片在电气或热物理等方面免受外力损害及外部环境的影响;同时通过封装使芯片的热膨胀系数与框架或基板的热膨胀系数相匹配,这样就能缓解由于热等外部环境的变化而产生的应力以及由于芯片发热而产生的应力,从而可防止芯片损坏失效。基于散热的要求,封装越薄越好,当芯片功耗大于2W时,在封装上需要增加散热片或热沉片,以增强其散热冷却功能;5~1OW时必须采取强制冷却手段。另一方面,封装后的芯片也更便于安装和运输。

(2)电气连接。封装的尺寸调整(间距变换)功能可由芯片的极细引线间距,调整到实装基板的尺寸间距,从而便于实装操作。例如从以亚微米(目前已达到0.1 3μm以下)为特征尺寸的芯片,到以10μm为单位的芯片焊点,再到以100μm为单位的外部引脚,最后剑以毫米为单位的印刷电路板,都是通过封装米实现的。封装在这里起着由小到大、由难到易、由复杂到简单的变换作用,从而可使操作费用及材料费用降低,而且能提高工作效率和可靠性,特别是通过实现布线长度和阻抗配比尽可能地降低连接电阻,寄生电容和电感来保证正确的信号波形和传输速度。

(3)标准规格化。规格通用功能是指封装的尺寸、形状、引脚数量、间距、长度等有标准规格,既便于加工,又便于与印刷电路板相配合,相关的生产线及生产设备都具有通用性。这对于封装用户、电路板厂家、半导体厂家都很方便,而且便于标准化。相比之下,裸芯片实装及倒装目前尚不具备这方面的优势。由于组装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的印刷电路板(PCB)的设计和制造,对于很多集成电路产品而言,组装技术都是非常关键的一环。

OPGA(Organic pin grid Array,有机管脚阵列)。这种封装的基底使用的是玻璃纤维,类似印刷电路板上的材料。此种封装方式可以降低阻抗和封装成本。OPGA封装拉近了外部电容和处理器内核的距离,可以更好地改善内核供电和过滤电流杂波。AMD公司的AthlonXP系列CPU大多使用此类封装。

mPGA,微型PGA封装,目前只有AMD公司的Athlon 64和英特尔公司的Xeon(至强)系列CPU等少数产品所采用,而且多是些高端产品,是种先进的封装形式。

CPGA也就是常说的陶瓷封装,全称为Ceramic PGA。主要在Thunderbird(雷鸟)核心和"Palomino"核心的Athlon处理器上采用。

FC-PGA封装是反转芯片针脚栅格阵列的缩写,这种封装中有针脚插入插座。这些芯片被反转,以至片模或构成计算机芯片的处理器部分被暴露在处理器的上部。通过将片模暴露出来,使热量解决方案可直接用到片模上,这样就能实现更有效的芯片冷却。为了通过隔绝电源信号和接地信号来提高封装的性能,FC-PGA 处理器在处理器的底部的电容放置区域(处理器中心)安有离散电容和电阻。芯片底部的针脚是锯齿形排列的。此外,针脚的安排方式使得处理器只能以一种方式插入插座。FC-PGA 封装用于奔腾 III 和英特尔 赛扬 处理器,它们都使用 370 针。

FC-PGA2 封装与 FC-PGA 封装类型很相似,除了这些处理器还具有集成式散热器 (IHS)。集成式散热器是在生产时直接安装到处理器片上的。由于 IHS 与片模有很好的热接触并且提供了更大的表面积以更好地发散热量,所以它显著地增加了热传导。FC-PGA2 封装用于奔腾 III 和英特尔赛扬处理器(370 针)和奔腾 4 处理器(478 针)。

OOI 是 OLGA 的简写。OLGA 代表了基板栅格阵列。OLGA 芯片也使用反转芯片设计,其中处理器朝下附在基体上,实现更好的信号完整性、更有效的散热和更低的自感应。OOI 有一个集成式导热器 (IHS),能帮助散热器将热量传给正确安装的风扇散热器。OOI 用于奔腾 4 处理器,这些处理器有 423 针。

"PPGA"的英文全称为"Plastic Pin Grid Array",是塑针栅格阵列的缩写,这些处理器具有插入插座的针脚。为了提高热传导性,PPGA 在处理器的顶部使用了镀镍铜质散热器。芯片底部的针脚是锯齿形排列的。此外,针脚的安排方式使得处理器只能以一种方式插入插座。

"S.E.C.C."是"Single Edge Contact Cartridge"缩写,是单边接触卡盒的缩写。为了与主板连接,处理器被插入一个插槽。它不使用针脚,而是使用"金手指"触点,处理器使用这些触点来传递信号。S.E.C.C. 被一个金属壳覆盖,这个壳覆盖了整个卡盒组件的顶端。卡盒的背面是一个热材料镀层,充当了散热器。S.E.C.C. 内部,大多数处理器有一个被称为基体的印刷电路板连接起处理器、二级高速缓存和总线终止电路。S.E.C.C. 封装用于有 242 个触点的英特尔奔腾II 处理器和有 330 个触点的奔腾II 至强和奔腾 III 至强处理器。

S.E.C.C.2 封装与 S.E.C.C. 封装相似,除了S.E.C.C.2 使用更少的保护性包装并且不含有导热镀层。S.E.C.C.2 封装用于一些较晚版本的奔腾II 处理器和奔腾 III 处理器(242 触点)。

"S.E.P."是"Single Edge Processor"的缩写,是单边处理器的缩写。"S.E.P."封装类似于"S.E.C.C."或者"S.E.C.C.2"封装,也是采用单边插入到Slot插槽中,以金手指与插槽接触,但是它没有全包装外壳,底板电路从处理器底部是可见的。"S.E.P."封装应用于早期的242根金手指的Intel Celeron 处理器。

PLGA是Plastic Land Grid Array的缩写,即塑料焊盘栅格阵列封装。由于没有使用针脚,而是使用了细小的点式接口,所以PLGA封装明显比以前的FC-PGA2等封装具有更小的体积、更少的信号传输损失和更低的生产成本,可以有效提升处理器的信号强度、提升处理器频率,同时也可以提高处理器生产的良品率、降低生产成本。目前Intel公司Socket 775接口的CPU采用了此封装。

CuPGA是Lidded Ceramic Package Grid Array的缩写,即有盖陶瓷栅格阵列封装。其与普通陶瓷封装最大的区别是增加了一个顶盖,能提供更好的散热性能以及能保护CPU核心免受损坏。AMD64系列CPU采用了此封装。

LED封装技术大都是在分立器件封装技术基础上发展与演变而来的,但却有很大的特殊性。一般情况下,分立器件的管芯被密封在封装体内,封装的作用主要是保护管芯和完成电气互连。而LED封装则是完成输出电信号,保...

1、投标报价单独封装,技术部分和商务部分分别封装。(重点在分别封装)2、后面封装要求又说商务部分及技术部分封装为一个包,(分别封装后,再进行并装)3、报价书单独封装于一个信封、U盘单独封装于一个信封,...

第一名:河南东尊装饰设计公司 东尊装饰设计公司创立于2010年,是一家拥有丰富经验,锐意进取,富...

1.芯片面积与封装面积之比为提高封装效率,尽量接近1:1

2.引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能

3.基于散热的要求,封装越薄越好

作为计算机的重要组成部分,CPU的性能直接影响计算机的整体性能。而CPU制造工艺的最后一步也是最关键一步就是CPU的封装技术,采用不同封装技术的CPU,在性能上存在较大差距。只有高品质的封装技术才能生产出完美的CPU产品。

由于电子整机和系统在航空、航天、计算机等领域对小型化、轻型化、薄型化等高密度组装要求的不断提高,在MCM的基础上,对于有限的面积,电子组装必然在二维组装的基础上向z方向发展,这就是所谓的三维(3D)封装技术,这是今后相当长时间内实现系统组装的有效手段。

实现3D封装主要有三种方法。一种是埋置型,即将元器件埋置在基板多层布线内或埋置、制作在基板内部。电阻和电容一般可随多层布线用厚、薄膜法埋置于多层基板中,而IC芯片一般要紧贴基板。还可以在基板上先开槽,将IC芯片嵌入,用环氧树脂固定后与基板平面平齐,然后实施多层布线,最上层再安装IC芯片,从而实现3D封装。第二种方法是有源基板型,这是用硅圆片IC(WSI)作基板时,先将WSI用一般半导体IC制作方法作一次元器件集成化,这就成了有源基板。然后再实施多层布线,顶层仍安装各种其他lC芯片或其他元器件,实现3D封装。这一方法是人们最终追求并力求实现的一种3D封装技术。第三种方法是叠层法,即将两个或多个裸芯片或封装芯片在垂直芯片方向上互连成为简单的3D封装。更多的是将各个已单面或双面组装的MCM叠装在一起,再进行上下多层互连,就可实现3D封装。其上下均可加热沉,这种3D结构又称为3D.MCM。由于3D的组装密度高,功耗大,基板多为导热性好的高导热基板,如硅、氮化铝和金刚石薄膜等。还可以把多个硅圆片层叠在一起,形成3D封装。

先进的叠层式3D封装技术

近几年来,先进的封装技术已在IC制造行业开始出现,如多芯片模块(MCM)就是将多个IC芯片按功能组合进行封装,特别是三维(3D)封装首先突破传统的平面封装的概念,组装效率高达200%以上。它使单个封装体内可以堆叠多个芯片,实现了存储容量的倍增,业界称之为叠层式3D封装;其次,它将芯片直接互连,互连线长度显著缩短,信号传输得更快且所受干扰更小;再则,它将多个不同功能芯片堆叠在一起,使单个封装体实现更多的功能,从而形成系统芯片封装新思路;最后,采用3D封装的芯片还有功耗低、速度快等优点,这使电子信息产品的尺寸和重量减小数十倍。正是由于3D封装拥有无可比拟的技术优势,加上多媒体及无线通信设备的使用需求,才使这一新型的封装方式拥有广阔的发展空间。

最常见的裸芯片叠层3D封装先将生长凸点的合格芯片倒扣并焊接在薄膜基板上,这种薄膜基板的材质为陶瓷或环氧玻璃,其上有导体布线,内部也有互连焊点,两侧还有外部互连焊点,然后再将多个薄膜基板进行叠装互连。

裸芯片叠层的工艺过程为:第一步,在芯片上生长凸点并进行倒扣焊接。如果采用金凸点,则由金丝成球的方式形成凸点,在250~400 ℃下,加压力使芯片与基板互连;若用铅锡凸点,则采用 Pb95Sn5(重量比)的凸点,这样的凸点具有较高的熔点,而不致在下道工艺过程中熔化。具体方法,先在低于凸点熔点的温度(180~250 ℃)下进行芯片和基板焊接,在这一温度下它们靠金属扩散来焊接;然后加热到250~400 ℃,在这一温度下焊料球熔化,焊接完毕。第一步的温度是经过成品率试验得到的,当低于150 ℃时断路现象增加;而当高于300 ℃时,则相邻焊点的短路现象增多。第二步,在芯片与基板之间0.05 mm的缝隙内填入环氧树脂胶,即进行下填料。第三步,将生长有凸点的基板叠装在一起,该基板上的凸点是焊料凸点,其成分为Pb/Sn或Sn/Ag,熔点定在200~240 ℃。这最后一步是将基板叠装后,再在230~250 ℃的温度下进行焊接。

MCM叠层的工艺流程与裸芯片叠层的工艺流程基本一致。除上述边缘导体焊接采用互连方式外,叠层3D封装还有多种互连方式,例如引线键合叠层芯片就是一种采用引线键合技术实现叠层互连的,该方法的适用范围比较广。此外,叠层互连工艺还有叠层载带、折叠柔性电路等方式。叠层载带是用载带自动键合(TAB)实现IC互连,可进而分为印刷电路板(PCB)叠层TAB和引线框架TAB。折叠柔性电路方式是先将裸芯片安装在柔性材料上,然后将其折叠,从而形成三维叠层的封装形式。

中国封装技术与国外封装技术的差距所在

1.封装技术人才严重短缺、缺少制程式改善工具的培训及持续提高培训的经费及手段。

2.先进的封装设备、封装材料及其产业链滞后,配套不全且质量不稳定。

(3)封装技术研发能力不足,生产工艺程序设计不周全,可操作性差,执行能力弱。

(4)封装设备维护保养能力欠伟,缺少有经验的维修工程师,且可靠性实验设备不齐全,失效分析(FA)能力不足。

(5)国内封装企业除个别企业外,普遍规模较小,从事低端产品生产的居多,可持续发展能力低,缺乏向高档发展的技术和资金。

(6)缺少团队精神,缺乏流程整合、持续改善、精细管理的精神,缺少现代企业管理的机制和理念。

半导体器件有许多封装形式,按封装的外形、尺寸、结构分类可分为引脚插入型、表面贴装型和高级封装三类。从DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技术指标一代比一代先进。总体说来,半导体封装经历了三次重大革新:第一次是在20世纪80年代从引脚插入式封装到表面贴片封装,它极大地提高了印刷电路板上的组装密度;第二次是在20世纪90年代球型矩阵封装的出现,满足了市场对高引脚的需求,改善了半导体器件的性能;芯片级封装、系统封装等是现在第三次革新的产物,其目的就是将封装面积减到最小。

所谓封装是指安装半导体集成电路芯片用的外壳,它不仅起着安放、固定、密封、保护芯片和增强电热性能的作用,而且还是沟通芯片内部世界与外部电路的桥梁-芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印制板上的导线与其他器件建立连接。因此,封装对CPU和其他LSI集成电路都起着重要的作用。新一代CPU的出现常常伴随着新的封装形式的使 用。芯片的封装技术已经历了好几代的变迁,从DIP、QFP、PGA、BGA到CSP再到MCM,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越 接近于1,适用频率越来越高,耐温性能越来越好,引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等。

微电子封装通常有五种功能,即电源分配、信号分配、散热通道、机械支撑和环境保护。

1.电源分配

微电子封装首先要能接通电源,使芯片与电路流通电流。其次,微电子封装的不同部位所

需的电源有所不同,要能将不同部位的电源分配恰当,以减少电源的不必要损耗,这在多层布

线基板上尤为重要。同时,还要考虑接地线的分配问题。

2.信号分配

为使电信号延迟尽可能减小,在布线时应尽可能使信号线与芯片的互连路径及通过封装的I/O引出的路径达到最短。对于高频信号,还应考虑信号间的串扰,以进行合理的信号分配布线和接地线分配。

3.散热通道

各种微电子封装都要考虑器件、部件长期工作时如何将聚集的热量散出的问题。不同的封装结构和材料具有不同的散热效果,对于功耗大的微电子封装,还应考虑附加热沉或使用强制风冷、水冷方式,以保证系统在使用温度要求的范围内能正常工作。

4.机械支撑

微电子封装可为芯片和其他部件提供牢固可靠的机械支撑,并能适应各种工作环境和条件的变化。

5.环境保护

半导体器件和电路的许多参数,如击穿电压、反向电流、电流放大系数、噪声等,以及器件的稳定性、可靠性都直接与半导体表面的状态密切相关。半导体器件和电路制造过程中的许

多工艺措施也是针对半导体表面问题的。半导体芯片制造出来后,在没有将其封装之前,始终

都处于周围环境的威胁之中。在使用中,有的环境条件极为恶劣,必须将芯片严加密封和包封。所以,微电子封装对芯片的环境保护作用显得尤为重要。

反映IC的发展水平,通常都是以IC的集成度及相应的特征尺寸为依据的。集成度决定着IC的规模,而特征尺寸则标志着工艺水平的高低。自20世纪70年代以来,IC的特征尺寸几乎每4年缩小一半。RAM、DRAM和MPU的集成度每年分别递增50%和35%,每3年就推出新一代DRAM。但集成度增长的速度快,特征尺寸缩小得慢,这样,又使IC在集成度提高的同时,单个芯片的面积也不断增大,大约每年增大13%。同时,随着IC集成度的提高和功能的不断增加,IC的I/O数也随之提高,相应的微电子封装的I/0引脚数也随之增加。例如,一个集成50万个门阵列的IC芯片,就需要一个700个.I/O引脚的微电子封装。这样高的I/0引脚数,要把IC芯片封装并引出来,若沿用大引脚节距且双边引出的微电子封装(如2.54 mmDIP),显然壳体大而重,安装面积不允许。从事微电子封装的专家必然要改进封装结构,如将双边引出改为四边引出,这就是后来的I,CCC、PL,CC和OFP,其I/O引脚节距也缩小到0.4 mm,甚至0.3mm,,随着IC的集成度和I/O数进一步增加,再继续缩小节距,这种QFP在工艺上已难以实施,或者组装焊接的成品率很低(如0.3mm的QFP组装焊接失效率竟高达6%e)。于是,封装的引脚由四边引出发展成为面阵引出,这样,与OFP同样的尺寸,节距即使为1mm,也能满足封装具有更多I/O数的IC的要求,这就是正在高速发展着的先进的BGA封装。

裸芯片技术有两种主要形式:一种是COB技术,另一种是倒装片技术(Flip chip)。

用COB技术封装的裸芯片是芯片主体和I/O端子在晶体上方,在焊接时将此裸芯片用导电/导热胶粘接在PCB上,凝固后,用 Bonder 机将金属丝(Al或Au)在超声、热压的作用下,分别连接在芯片的I/O端子焊区和PCB相对应的焊盘上,测试合格后,再封上树脂胶。 与其它封装技术相比,COB技术有以下优点:价格低廉;节约空间;工艺成熟。COB技术也存在不足,即需要另配焊接机及封装机,有时速度跟不上;PCB贴片对环境要求更为严格;无法维修等。

Flip chip,又称为倒装片,与COB相比,芯片结构和I/O端(锡球)方向朝下,由于I/O引出端分布于整个芯片表面,故在封装密度和处理速度上Flip chip已达到顶峰,特别是它可以采用类似SMT技术的手段来加工,故是芯片封装技术及高密度安装的最终方向。90年代,该技术已在多种行业的电子产品中加以推广,特别是用于便携式的通信设备中。裸芯片技术是当今最先进的微电子封装技术。随着电子产品体积的进一步缩小,裸芯片的应用将会越来越广泛。

LED封装技术大全

LED封装技术大全

LED封装技术大全

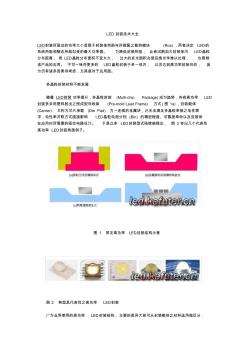

LED 封装技术大全 LED封装所驱动的功率大小受限于封装体热阻与所搭配之散热模块 (Rca) ,两者决定 LED的 系统热阻和稳态所能忍受的最大功率值。 为降低封装热阻, 业者试图加大封装体内 LED晶粒 分布距离, 然 LED晶粒分布面积不宜太大, 过大的发光面积会使后续光学难以处理, 也限制 该产品的应用。 不可一味将更多的 LED晶粒封装于单一体内, 以求达到高功率封装目的, 因 为仍有诸多因素待考虑,尤其是对于应用面。 多晶粒封装材料不断发展 随着 LED封装 功率提升,多晶粒封装 (Multi-chip Package)成为趋势,传统高功率 LED 封装多采用塑料射出之预成型导线架 (Pre-mold Lead Frame) 方式 (图 1a),封装载体 (Carrier) 又称为芯片承载 (Die Pad),为一连续的金属块,已无法满足多晶粒串接之电性需 求,电性串并联方式直

大功率LED封装技术

大功率LED封装技术

大功率LED封装技术

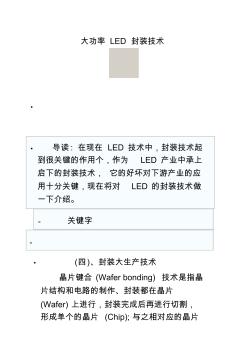

大功率 LED 封装技术 导读 : 在现在 LED 技术中,封装技术起 到很关键的作用个,作为 LED 产业中承上 启下的封装技术, 它的好坏对下游产业的应 用十分关键,现在将对 LED 的封装技术做 一下介绍。 o 关键字 o (四)、封装大生产技术 晶片键合 (Wafer bonding) 技术是指晶 片结构和电路的制作、封装都在晶片 (Wafer) 上进行,封装完成后再进行切割, 形成单个的晶片 (Chip); 与之相对应的晶片 键合 (Die bonding) 是指晶片结构和电路在 晶片上完成后,即进行切割形成晶片 (Die), 然后对单个晶片进行封装 (类似现在的 LED 封装工艺 ),如图 8 所示。很明显,晶 片键合封装的效率和质量更高。由于封装 费用在 LED 器件制造成本中占了很大比 例,因此,改变现有的 LED 封装形式 (从 晶片键合到晶片键合 ),将大大降低封装制

关于LGA封装技术与插座类型的区别

过去英特尔处理器的封装技术采用的是Socket,也被称为Socket T,采用的是针状插接技术,如Socket 478。而LGA的封装技术则是采用的点接触技术(触点)。说它是“跨越性的技术革命”,主要在于它用金属触点式封装技术(LGA)取代了过去的针状插脚式封装技术(Socket)。

由于人们对封装技术与插座类型存在一些误解,常常把封装技术与插座类型混淆。

下面我来解释一下封装技术与插座类型的区别。

根据电子分类,电子产品的封装与相对应的插座类型不属于同一类别,前者属于电子产品封装技术,后者属于机械类。

根据英特尔处理器的封装技术标准,Land Grid Array 栅格阵列式封装采用的是点接触技术。

而与之相对应的则是弹性针状式插座。

因此不能用Land Grid Array 栅格阵列式封装技术混淆在弹性针状式插座上。由于它们既不是同一类别,又不是同一属性,一个属于电子产品,一个属于电子配件;一个属于电子产品的封装技术,一个属于机械类的插座。因此机械类弹性针状式插座用Socket更确切,而不能用Land Grid Array 栅格阵列式封装技术来替代。2100433B

1、BGA封装技术

BGA封装技术诞生于20世纪90年代,其中文全称为焊球阵列封装技术,由于已经有了较长的发展历程,因而在目前的应用实践中有着较高的技术成熟度,通过球柱形焊点阵列进行I/O端与基板的封装是其主要的封装原理。相较于其他常见微电子封装技术,BGA封装技术的主要优势在于阵列密度高、组装成品率高。在塑料焊球阵列、陶瓷焊球阵列、金属焊球阵列等多种BGA封装技术中,装芯片焊球阵列封装将是未来BGA技术的主要发展方向。

2、3D封装技术

3D封装技术是伴随着移动互联网的发展而逐渐兴起的,目前主要应用于手持设备的高密度立体式组装之中,是同时满足多个芯片组立体式封装需求的有效途径。在现阶段市面上常见的各种封装技术中,3D封装技术具备的主要技术优势在于功能性丰富、封装密度高、电性能热性能突出。

3、表面封装技术

钎焊技术是目前使用最广的一种微电子表面封装技术,根据具体的衔接需要,将需要衔接的物体表面的电子元件与指定的焊盘进行钎焊,使原件与焊盘之间产生电路功能是钎焊技术的主要封装原理。此种焊接方式下,原件与焊盘的连接是极为可靠的;与此同时,软钎焊技术所使用的钎焊,其内包含的钎剂对于金属表面杂质的去除效果极佳,这对于焊接过程中钎料润滑度的增加是十分有利的,因而,相较于其他微电子封装技术,钎焊技术的封装速度明显更快。

我们都知道鸟笼是用竹棒把上下两块木板撑出一个空间,鸟就生活在这里面。我们将要说到的覆晶封装和鸟笼是有相似之处的。下面我们就来看一下什么是覆晶封装技术。

我们通常把晶片经过一系列工艺后形成了电路结构的一面称作晶片的正面。原先的封装技术是在衬底之上的晶片的正面是一直朝上的,而覆晶技术是将晶片的正面反过来,在晶片(看作上面那块板)和衬底(看作下面那块板)之间及电路的外围使用凸块(看作竹棒)连接,也就是说,由晶片、衬底、凸块形成了一个空间,而电路结构(看作鸟)就在这个空间里面。这样封装出来的芯片具有体积小、性能高、连线短等优点。

随着半导体业的迅速发展,覆晶封装技术势必成为封装业的主流。典型的覆晶封装结构是由凸块下面的冶金层、焊点、金属垫层所构成,因此冶金层在元件作用时的消耗将严重影响到整个结构的可靠度和元件的使用寿命。