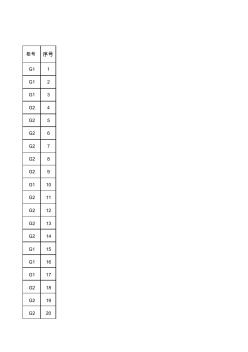

第1章 高速数字电路的PDN 1

1.1 PDN与SI、PI和EMI 1

1.1.1 PDN是SI、PI和EMI的公共互连基础 1

1.1.2 优良的PDN设计是SI、PI和EMI的基本保证 1

1.2 高速数字电路的PDN拓扑结构 3

1.3 基于目标阻抗的PDN设计 4

1.3.1 目标阻抗的定义 4

1.3.2 基于目标阻抗的PDN设计方法 6

1.3.3 利用目标阻抗计算去耦电容的电容量 8

1.4 基于功率传输的PDN设计方法 9

1.4.1 稳压电源电路的反应时间 10

1.4.2 去耦电容的去耦时间 10

1.4.3 电源系统的输出阻抗 11

1.4.4 利用电源驱动的负载计算电容量 12

1.5 平面PDN的一维分布模型 12

1.5.1 去耦网络的瞬态响应 12

1.5.2 去耦网络的稳态响应 13

1.5.3 功率传输延迟的估算 14

第2章 PDN中的电阻 16

2.1 电阻的基本特性 16

2.1.1 电阻的u-i特性 16

2.1.2 电阻的串联和并联 17

2.2 高速数字电路中的电阻 19

2.2.1 电阻的阻抗频率特性 19

2.2.2 互连线的电阻 23

2.2.3 单位长度电阻 27

2.2.4 方块电阻 29

2.2.5 非理想互连与电源/地平面突变的影响 29

2.2.6 趋肤效应的影响 30

第3章 PDN中的电容 32

3.1 电容的基本特性 32

3.1.1 电容的电容量 32

3.1.2 电容的电压-电流关系 33

3.1.3 电容的串联和并联 34

3.2 电容的频率特性 35

3.2.1 电容的阻抗频率特性 35

3.2.2 电容的衰减频率特性 36

3.3 电容的ESR和ESL特性 37

3.4 片状电容的使用 38

3.4.1 片状电容的选择 38

3.4.2 片状电容的PCB设计注意事项 38

3.5 低ESL的电容 41

3.5.1 低ESL电容的结构 41

3.5.2 低ESL电容的阻抗频率特性 42

3.6 片状三端子电容 43

3.6.1 片状三端子电容的频率特性 43

3.6.2 使用三端子电容减小ESL 45

3.6.3 三端子电容的PCB布局与等效电路 45

3.6.4 三端子电容的应用 47

3.7 X2Y电容 48

3.7.1 采用X2Y电容替换穿心式电容 48

3.7.2 X2Y电容的封装形式和尺寸 48

3.7.3 X2Y电容的应用与PCB布局 49

3.8 可藏于PCB基板内的电容 51

3.9 PCB的电容 52

3.9.1 PCB的平行板电容 52

3.9.2 PCB的导线电容 53

3.9.3 PCB的导线互容 54

3.9.4 PCB的过孔电容 57

3.10 埋入式电容 58

3.10.1 埋入式电容技术简介 58

3.10.2 埋入式电容技术的应用 60

3.11 IC封装的电容 62

第4章 PDN中的电感 64

4.1 电感的基本特性 64

4.1.1 电感的电感量 64

4.1.2 电感的电压-电流关系 65

4.1.3 电感的串联和并联 65

4.2 电感的频率特性 67

4.2.1 电感的阻抗频率特性 67

4.2.2 电感的Q值频率特性 67

4.2.3 电感的电感值频率特性 69

4.3 电感的电感值DC电流特性 70

4.4 电感的选择 71

4.5 互感 72

4.5.1 互感现象 72

4.5.2 耦合系数 73

4.5.3 耦合电感上的电压-电流关系 73

4.5.4 两相邻通路与导线间的“互感耦合” 74

4.6 局部电感 75

4.6.1 局部自感 75

4.6.2 局部互感 75

4.7 回路电感 76

4.7.1 导线回路的电感 76

4.7.2 回路面积对电感的影响 77

4.7.3 环形线圈的回路电感 78

4.7.4 两根相邻导线的回路电感 78

4.8 PCB的电感 78

4.8.1 PCB导线的电感 78

4.8.2 PCB过孔的电感 80

4.8.3 PCB导线的互感 81

4.8.4 PCB电源/地平面电感 82

4.9 IC封装的电感 82

4.10 贴装电感 85

4.10.1 电容贴装电感 85

4.10.2 IC贴装电感 86

4.11 电感引起的“地弹”及其控制 86

4.11.1 “地弹” 86

4.11.2 “地弹”的控制 88

4.12 同时开关噪声(SSN) 90

4.12.1 SSN的成因 90

4.12.2 片上开关 91

4.12.3 片外开关 93

4.12.4 降低SSN的一些措施 94

4.13 LC电路的阻抗特性 96

4.13.1 LC串联电路的阻抗特性 96

4.13.2 LC并联电路的阻抗特性 96

第5章 PDN中的PCB电源/地平面 98

5.1 PCB电源/地平面的功能和设计原则 98

5.1.1 PCB电源/地平面的功能 98

5.1.2 PCB电源/地平面的设计原则 99

5.2 PCB电源/地平面叠层和层序 101

5.2.1 4层板的电源/地平面设计 101

5.2.2 6层板的电源/地平面设计 103

5.2.3 8层板的电源/地平面设计 105

5.2.4 10层板的电源/地平面设计 107

5.3 PCB电源/地平面的叠层电容 109

5.4 PCB电源/地平面的中间介质的影响 110

5.5 PCB电源/地平面的层耦合 111

5.6 PCB电源/地平面的谐振 112

5.7 电源平面上的电源岛结构 113

5.8 利用EBG结构抑制PCB电源/地平面的SSN 114

5.8.1 EBG结构简介 114

5.8.2 EBG结构的电路模型 115

5.8.3 EBG的单元结构 118

5.8.4 基于Sierpinski曲线的分形EBG结构 130

5.8.5 平面级联式EBG结构 132

5.8.6 选择性内插式EBG结构 133

5.8.7 多周期平面的EBG结构 134

5.8.8 垂直级联式EBG结构 135

5.8.9 嵌入多层螺旋平面的EBG结构 139

5.8.10 接地层开槽隔离型EBG结构 139

5.8.11 狭缝型UC-EBG电源平面 142

5.8.12 嵌入螺旋谐振环结构的电源平面 143

第6章 PDN中的去耦电路 145

6.1 去耦电路的结构与特性 145

6.1.1 去耦电路的基本结构 145

6.1.2 数字IC电源噪声的产生 147

6.1.3 测量去耦电路性能的测量点 149

6.1.4 去耦电路的插入损耗测量 149

6.2 插入损耗特性 150

6.2.1 电容的插入损耗特性 150

6.2.2 电感和铁氧体磁珠的插入损耗特性 152

6.3 影响电容噪声抑制效果的因素 153

6.3.1 电容频率特性的影响 153

6.3.2 噪声路径与电容的安装位置 154

6.3.3 外围电路阻抗的影响 160

6.3.4 电容的并联和反谐振 161

6.4 LC滤波器(去耦电路) 165

6.4.1 使用一个电感的去耦电路 165

6.4.2 电感器的插入损耗 166

6.4.3 铁氧体磁珠的插入损耗 167

6.4.4 LC滤波器的插入损耗特性 171

6.4.5 使用电感时的注意事项 175

6.5 使用去耦电容抑制电源电压波动 176

6.5.1 数字IC的电流和电压波动 176

6.5.2 电源阻抗和电压波动之间的关系 176

6.5.3 电压波动计算模型 177

6.5.4 抑制电流波动的尖峰 179

6.5.5 抑制脉冲宽度较宽的电流波动 180

6.6 使用去耦电容降低IC的电源阻抗 181

6.6.1 电源阻抗的计算模型 181

6.6.2 IC电源阻抗的计算 182

6.6.3 电容靠近IC放置的允许距离 183

6.7 去耦电容的组合特性 187

6.7.1 去耦电容的电流供应模式 187

6.7.2 IC电源的目标阻抗 187

6.7.3 去耦电容组合的阻抗特性 188

6.7.4 PCB上的目标阻抗 190

6.8 去耦电容的容量计算 192

6.8.1 计算去耦电容容量的模型 192

6.8.2 确定目标阻抗 192

6.8.3 确定大容量电容的容量 193

6.8.4 确定板电容的容量 194

6.8.5 确定板电容的安装位置 195

6.8.6 减少ESLcap 195

6.9 m"para" label-module="para">

6.9.1 组合多个电容达到m"para" label-module="para">

6.9.2 m"para" label-module="para">

6.10 去耦电容的选择 202

第7章 PDN中的电压调整模块(VRM) 207

7.1 DC-DC开关稳压器电路 207

7.1.1 DC-DC转换器的拓扑结构 207

7.1.2 DC-DC转换器PCB布局的一般原则 211

7.1.3 DC-DC转换器PCB布局的注意事项 213

7.1.4 减小DC-DC转换器中的地弹 218

7.1.5 DC-DC开关型降压稳压器设计实例 225

7.1.6 负载点DC-DC转换器 228

7.2 线性稳压器电源电路 231

7.2.1 线性稳压器与开关稳压器的差异 231

7.2.2 LDO线性稳压器简介 234

7.2.3 选择LDO线性稳压器的基本原则 236

7.2.4 LDO线性稳压器电容选型 237

7.2.5 LDO线性稳压器设计实例 246

7.3 模数混合系统的电源电路结构 248

7.3.1 模拟前端小信号检测和放大电路的供电电路 248

7.3.2 ADC和DAC电源电路的结构形式 250

7.3.3 混合IC电源电路 251

7.3.4 模数混合系统中的PCB电源/地平面设计要点 254

第8章 设计实例:FPGA的PDN设计 263

8.1 FPGA的PDN模型 263

8.1.1 FPGA的PDN通用模型 263

8.1.2 简化的FPGA的PDN模型 265

8.2 FPGA的供电要求 265

8.3 FPGA的PDN设计和验证 266

8.3.1 确定FPGA的参数 266

8.3.2 去耦网络设计 269

8.3.3 模拟 270

8.3.4 性能测量 271

8.3.5 优化去耦网络设计 273

8.3.6 存在问题的分析和改进 278

8.4 VirtexTM-5 FPGA的PDN设计实例 279

8.4.1 VirtexTM-5 FPGA的VRM 279

8.4.2 必需的PCB去耦电容 281

8.4.3 替代电容 282

8.4.4 PCB设计检查项目 283

8.4.5 VirtexTM-5的PCB布局实例 288

8.5 仿真工具 289

8.5.1 常用的一些PDN设计和仿真EDA工具 289

8.5.2 Altera PDN设计工具 290

8.5.3 TI公司的FPGA电源管理解决方案和设计工具 296

8.6 FPGA电源电路设计实例 300

8.6.1 Xilinx"para" label-module="para">

8.6.2 Xilinx"para" label-module="para">

8.6.3 Xilinx"para" label-module="para">

8.6.4 Xilinx"para" label-module="para">

8.6.5 Altera"para" label-module="para">

8.6.6 Altera"para" label-module="para">

8.7 多电源系统的监控和时序控制 328

8.7.1 电源时序控制和跟踪类型 328

8.7.2 多电源系统的监控和时序控制设计实例 329

8.7.3 模拟电压和电流监控 331

8.7.4 时序控制和监控的结合 331

8.7.5 电源余量微调 332

8.7.6 开关调节器的同步 334

参考文献 335 2100433B

电厂图书目录

电厂图书目录

电缆分配网络意外带电之防范

电缆分配网络意外带电之防范