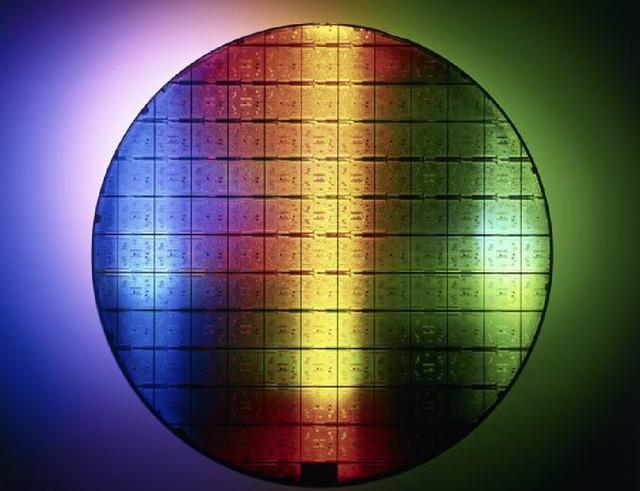

晶圆工艺文献

圆钢弯曲施工工艺

圆钢弯曲施工工艺

圆钢弯曲施工工艺

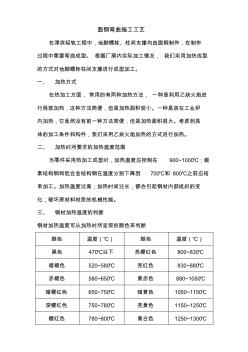

圆钢弯曲施工工艺 在津滨轻轨工程中,地脚螺栓、柱间支撑均由圆钢制作,在制作 过程中需要弯曲成型。 根据厂房内实际加工情况, 我们采用加热成型 的方式对地脚螺栓柱间支撑进行成型加工。 一、 加热方式 在热加工方面, 常用的有两种加热方法, 一种是利用乙炔火焰进 行局部加热,这种方法简便,但是加热面积较小。一种是放在工业炉 内加热,它虽然没有前一种方法简便,但是加热面积很大。考虑到具 体的加工条件和构件,我们采用乙炔火焰加热的方式进行加热。 二、 加热时所要求的加热温度范围 当零件采用热加工成型时,加热温度应控制在 900~1000℃;碳 素结构钢和低合金结构钢在温度分别下降到 700℃和 800℃之前应结 束加工。加热温度过高,加热时间过长,都会引起钢材内部组织的变 化,破坏原材料材质的机械性能。 三、 钢材加热温度的判断 钢材加热温度可从加热时所呈现的颜色来判断 颜色 温度(℃) 颜色 温

圆柱模施工工艺

圆柱模施工工艺

圆柱模施工工艺

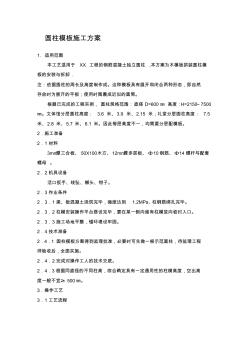

圆柱模板施工方案 1. 适用范围 本工艺适用于 XX 工程的钢筋混凝土独立圆柱 ,本方案为木模板拼装圆柱模 板的安装与拆卸 . 注:依据圆柱的周长及高度制作成。这种模板具有展开和闭合两种形态,即自然 存放时为展开的平板;使用时围裹成近似的圆筒。 根据已完成的工程实例, 圆柱规格范围:直径 D=600 ㎜ 高度:H=2150~7500 ㎜。文体馆分层圆柱高度: 3.6 米、3.9 米、2.15 米;礼堂分层圆柱高度: 7.5 米、2.8 米、5.7 米、6.1 米。因此每层高度不一,均需要分层配模板。 2.施工准备 2.1材料 3mm厚三合板、 50X100木方、12mm厚多层板、Φ10钢筋、Φ14螺杆与配套 螺母 。 2.2机具设备 活口扳手、线坠、榔头、钳子。 2.3作业条件 2.3.1梁、板混凝土浇筑完毕,强度达到 1.2MPa,柱钢筋绑扎完毕。 2.3.2柱模安装操作平台搭设完毕,