CMOS门电路

由单极型MOS管构成的门电路称为Mos门电路。MOS电路具有制造工艺简单、功耗低、集成度高、电源电压使用范围宽、抗干扰能力强等优点,特别适用于大规模集成电路。MOS门电路按所用MOS管的不同可分为三种类型:第一种是由PMOS管构成的PMOS门电路,其工作速度较低;第二种是由NMOS管构成的NMOS门电路,工作速度比PMOS电路要高,但比不上TTL电路;第三种是由PMOS管和NMOS管两种管子共同组成的互补型电路,称为CMOS电路,CMOS电路的优点突出,其静态功耗极低,抗干扰能力强,工作稳定可靠且开关速度也大大高于NMOS和PMOS电路,故得到了广泛应用。

MOS管主要参数

1、开启电压VT

·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;

·标准的N沟道MOS管,VT约为3~6V;

·通过工艺上的改进,可以使MOS管的VT值降到2~3V。

2、直流输入电阻RGS

·即在栅源极之间加的电压与栅极电流之比

·这一特性有时以流过栅极的栅流表示

·MOS管的RGS可以很容易地超过1010Ω。

3、漏源击穿电压BVDS

·在VGS=0(增强型)的条件下,在增加漏源电压过程中使ID开始剧增时的VDS称为漏源击穿电压BVDS

·ID剧增的原因有下列两个方面:(1)漏极附近耗尽层的雪崩击穿,(2)漏源极间的穿通击穿。

·有些MOS管中,其沟道长度较短,不断增加VDS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后,源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的ID4、栅源击穿电压BVGS

·在增加栅源电压过程中,使栅极电流IG由零开始剧增时的VGS,称为栅源击穿电压BVGS。

5、低频跨导gm

·在VDS为某一固定数值的条件下,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导

·gm反映了栅源电压对漏极电流的控制能力

·是表征MOS管放大能力的一个重要参数

·一般在十分之几至几mA/V的范围内

6、导通电阻RON

·导通电阻RON说明了VDS对ID的影响,是漏极特性某一点切线的斜率的倒数

·在饱和区,ID几乎不随VDS改变,RON的数值很大,一般在几十千欧到几百千欧之间

·由于在数字电路中,MOS管导通时经常工作在VDS=0的状态下,所以这时的导通电阻RON可用原点的RON来近似

·对一般的MOS管而言,RON的数值在几百欧以内

7、极间电容

·三个电极之间都存在着极间电容:栅源电容CGS、栅漏电容CGD和漏源电容CDS

·CGS和CGD约为1~3pF

·CDS约在0.1~1pF之间

8、低频噪声系数NF

·噪声是由管子内部载流子运动的不规则性所引起的

·由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化

·噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)

·这个数值越小,代表管子所产生的噪声越小

·低频噪声系数是在低频范围内测出的噪声系数

·场效应管的噪声系数约为几个分贝,它比双极性三极管的要小

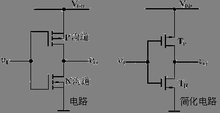

CMOS反相器

CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件。CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。此外,几乎所有的超大规模存储器件,以及PLD器件都采用CMOS 艺制造,且费用较低。早期生产的CMOS门电路为4000系列,随后发展为4000B系列。当前与TTL兼容的CMO器件如74HCT系列等可与TTL器件交换使用。MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。由N沟道和P沟道两种MOSFET组成的电路称为互补MOS或CMOS电路。CMOS反相器电路,由两只增强型MOSFET组成,其中一个为N沟道结构,另一个为P沟道结构。为了电路能正常工作,要求电源电压VDD大于两个管子的开启电压的绝对值之和,即VDD>(VTN+|VTP|)。

CMOS门电路

1、与非门电路:包括两个串联的N沟道增强型MOS管和两个并联的P沟道增强型MOS管。每个输入端连到一个N沟道和一个P沟道MOS管的栅极。当输入端A、B中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B全为高电平时,才会使两个串联的NMOS管都导通,使两个并联的PMOS管都截止,输出为低电平。因此,这种电路具有与非的逻辑 功能,即n个输入端的与非门必须有n个NMOS管串联和n个PMOS管并联。

2.或非门电路:包括两个并联的N沟道增强型MOS管和两个串联的P沟道增强型MOS管。当输入端A、B中只要有一个为高电平时,就会使与它相连的NMOS管导通,与它相连的PMOS管截止,输出为低电平;仅当A、B全为低电平时,两个并联NMOS管都截止,两个串联的PMOS管都导通,输出为高电平。因此,这种电路具有或非的逻辑功能,其逻辑表达式为。显然,n个输入端的或非门必须有n个NMOS管并联和n个PMOS管并联。比较CMOS与非门和或非门可知,与非门的工作管是彼此串联的,其输出电压随管子个数的增加而增加;或非门则相反,工作管彼此并联,对输出电压不致有明显的影响。因而或非门用得较多。

3、异或门电路:它由一级或非门和一级与或非门组成。或非门的输出。而与或非门的输出L即为输入A、B的异或如在异或门的后面增加一级反相器就构成异或非门,由于具有的功能,因而称为同或门。

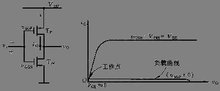

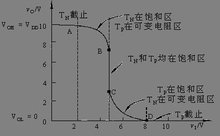

CMOS传输门

MOSFET的输出特性在原点附近呈线性对称关系,因而它们常用作模拟开关。模拟开关广泛地用于取样--保持电路、斩波电路、模数和数模转换电路等。下面着重介绍CMOS传输门。所谓传输门(TG)就是一种传输模拟信号的模拟开关。CMOS传输门由一个P沟道和一个N沟道增强型MOSFET并联而成,如上图所示。TP和TN是结构对称的器件,它们的漏极和源极是可互换的。设它们的开启电压|VT|=2V且输入模拟信号的变化范围为-5V到+5V。为使衬底与漏源极之间的PN结任何时刻都不致正偏,故TP的衬底接+5V电压,而TN的衬底接-5V电压。两管的栅极由互补的信号电压(+5V和-5V)来控制,分别用C和表示。传输门的工作情况如下:当C端接低电压-5V时TN的栅压即为-5V,vI取-5V到+5V范围内的任意值时,TN均不导通。同时、TP的栅压为+5V,TP亦不导通。可见,当C端接低电压时,开关是断开的。为使开关接通,可将C端接高电压+5V。此时TN的栅压为+5V,vI在-5V到+3V的范围内,TN导通。同时TP的棚压为-5V,vI在-3V到+5V的范围内TP将导通。由上分析可知,当vI<-3V时,仅有TN导通,而当vI>+3V时,仅有TP导通当vI在-3V到+3V的范围内,TN和TP两管均导通。进一步分析还可看到,一管导通的程度愈深,另一管的导通程度则相应地减小。换句话说,当一管的导通电阻减小,则另一管的导通电阻就增加。由于两管系并联运行,可近似地认为开关的导通电阻近似为一常数。这是CMOS传输门的优点。在正常工作时,模拟开关的导通电阻值约为数百欧,当它与输入阻抗为兆欧级的运放串接时。可以忽略不计。CMOS传输门除了作为传输模拟信号的开关之外,也可作为各种逻辑电路的基本单元电路。