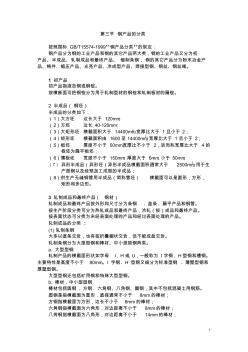

指标含义表现单位

存储容量在一个存储器中可以容纳的存储单元总数存储空间的大小 字数,字节数

存取时间启动到完成一次存储器操作所经历的时间 主存的速度 ns

存储周期连续启动两次操作所需间隔的最小时间 主存的速度 ns

存储器带宽单位时间里存储器所存取的信息量, 它是衡量数据传输速率的重要技术指标,单位是b∕s( 位/秒)或B∕S(字节/秒)。

存放一个机器字的存储单元,通常称为字存储单元,相应的单元地址叫字地址。而存放一个字节的单元,称为字节存储单元,相应的地址称为字节地址。如果计算机中可编址的最小单位是字存储单元,则该计算机称为按字编址的计算机。如果计算机中可编址的最小单

位是字节,则该计算机称为按字节编址的计算机。一个机器字可以包含数个字节,所以一个存储单元也可以包含数个能够单独编址的字节地址。例如,PDP-11系列计算机,一个16位二进制的字存储单元可存放两个字节,可以按字地址寻址,也可以按字节地址寻址。当用字节地址寻址时,16位的存储单元占两个字节地址。

容量

在一个存储器中容纳的存储单元总数通常称为该存储器的存储容量。存储容量用字数或字节数(B)来表示,如64K字,512KB,10MB。外存中为了表示更大的存储容量,采用MB,GB,TB等单位。其中1KB=2^10B,1MB=2^20B,1GB=2^30B,1TB=2^40B。B表示字节,一个字节定义为8个二进制位,所以计算机中一个字的字长通常为8的倍数。存储容量这一概念反映了存储空间的大小。

时间

又称存储器访问时间或读∕写时间,是指从启动一次存储器操作到完成该操作所经历的时间。具体讲,从一次读操作命令发出到该操作完成,将数据读入数据缓冲寄存器为止所经历的时间,即为存储器存取时间。

周期

是指连续启动两次独立的存储器操作(如连续两次读操作)所需间隔的最小时间。通常,存储周期略大于存储时间,其时间单位为ns

-