教学计算机的内存储器组成与设计

(1)静态存储器的存储原理和芯片内部结构(P207)

(2)教学计算机内存储器的组成与设计

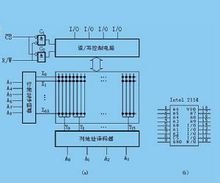

地址总线:记为AB15~AB0,统一由地址寄存器AR驱动,地址寄存器AR只接收ALU输出的信息。

控制总线:控制总线的信号由译码器74LS139给出,功能是指出总线周期的类型:

(1)内存写周期用MMW信号标记

(2)内存读周期用MMR信号标记

(3)外设(接口)写周期用IOW信号标记

(4)外设(接口)读周期用IOR信号标记

(5)内存在工作用MMREQ信号标记

(6)外设在工作用IOREQ信号标记

(7)写控存周期用SWA信号标记

数据总线:分为内部数据总线IB与外部数据总线DB两部分。主要完成计算机各功能部件之间的数据传送。设计总线的核心技术是要保证在任何时刻只能把一组数据发送到总线上,却允许一个和多个部件同时接受总线上的信息。所用的电路通常为三态门电路。

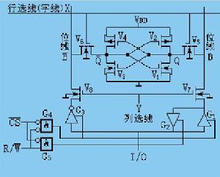

系统时钟及时序:教学机晶振1.8432MHz,3分频后用614.4KHz的时钟作为系统主时钟,使CPU、内存、IO同步运行。CPU内部的有些寄存器用时钟结束时的上升沿完成接受数据,而通用寄存器是用低电平接收的。内存或I/O读写操作时,每个总线周期由两个时钟组成,第一个时钟,称为地址时间,用于传送地址;第二个时钟,称为数据时间,用于读写数据

静态存储器的字位扩展:

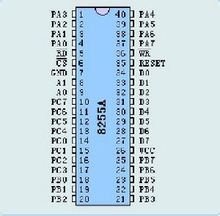

教学计算机的内存储器用静态存储器芯片实现,由2K字的ROM区和2K字RAM区组成。内存字长16位,按字寻址。ROM由74LS2716只读存储器ROM(每片2048个存储单元,每单元为8位二进制位)两片完成字长的扩展。地址分配在:0~2047RAM由74LS6116随机存储器RAM(每片2048个存储单元,每单元为8位二进制位)两片完成字长的扩展。地址分配在:2048~4095。

静态存储器地址分配:

为访问2048个存储单元,要用11位地址,把地址总线的低11位地址送到每个存储器芯片的地址引脚;对地址总线的高位进行译码,译码信号送到各存储器芯片的/CS引脚,在按字寻址的存储器系统中实现按字节读写。

动态存储器的定期刷新:在不进行读写操作时,DRAM存储器的各单元处于断电状态,由于漏电的存在,保存在电容CS上的电荷会慢慢地漏掉,为此必须定时予以补充,称为刷新操作。

(1)动态存储器的组成:由单个MOS管来存储一位二进制信息。信息存储在MOS管的源极的寄生电容CS中。

写数据时:字线为高电平,T导通。

写"1"时,位线(数据线)为低电平,VDD(电源)将向电容充电

写"0时,位线(数据线)为高电平,若电容存储了电荷,则将会使电容完成放电,就表示存储了"0"。

读数据时:先使位线(数据线)变为高电平,当字线高电平到来时T导通,若电容原存储有电荷(是"1"),则电容就要放电,就会使数据线电位由高变低;若电容没有存储电荷(是"0"),则数据线电位不会变化。检测数据线上电位的变化就可以区分读出的数据是1还是0。

注意

①读操作使电容原存储的电荷丢失,因此是破坏性读出。为保持原记忆内容,必须在读操作后立刻跟随一次写入操作,称为预充电延迟。

②向动态存储器的存储单元提供地址,是先送行地址再送列地址。原因就是对动态存储器必须定时刷新(如2ms),刷新不是按字处理,而是每次刷新一行,即为连接在同一行上所有存储单元的电容补充一次能量。

③在动态存储器的位线上读出信号很小,必须接读出放大器,通常用触发器线路实现。

④存储器芯片内部的行地址和列地址锁存器分先后接受行、列地址。

⑤RAS、CAS、WE、Din、Dout时序关系