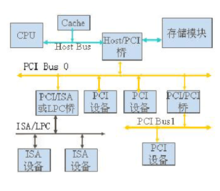

PCI总线是一种树型结构,并且独立于CPU总线,可以和CPU总线并行操作。PCI总线上可以挂接PCI设备和PCI桥片,PCI总线上只允许有一个PCI主设备,其他的均为PCI 从设备,而且读写操作只能在主从设备之间进行,从设备之间的数据交换需要通过主设备中转。PCI总线结构如下图所示。

在处理器系统中,含有PCI总线和PCI总线树这两个概念。这两个概念并不相同,在一颗PCI总线树中可能具有多条PCI总线,而具有血缘关系的PCI总线组成一颗PCI总线树。PCI总线由HOST主桥或者PCI桥管理,用来连接各类设备,如声卡、网卡和IDE接口卡等。在一个处理器系统中,可以通过PCI桥扩展PCI总线,并形成具有血缘关系的多级PCI总线,从而形成PCI总线树型结构。在处理器系统中有几个HOST主桥,就有几颗这样的PCI总线树,而每一颗PCI总线树都与一个PCI总线域对应。

与HOST主桥直接连接的PCI总线通常被命名为PCI总线0。考虑到在一个处理器系统中可能有多个主桥。

PCI总线取代了早先的ISA总线。当然与在PCI总线后面出现专门用于显卡的AGP总线,与现在的PCI Express总线相比,功能没有那么强大,但是PCI能从1992用到现在,说明他有许多优点,比如即插即用(Plug and Play)、中断共享等。在这里我们对PCI总线做一个深入的介绍。

从数据宽度上看,PCI总线有32bit、64bit之分;从总线速度上分,有33MHz、66MHz两种。目前流行的是32bit @ 33MHz,而64bit系统正在普及中。改良的PCI系统,PCI-X,最高可以达到64bit @ 133MHz,这样就可以得到超过1GB/s的数据传输速率。如果没有特殊说明,以下的讨论以32bit @ 33MHz为例。

不同于ISA总线,PCI总线的地址总线与数据总线是分时复用的。这样做的好处是,一方面可以节省接插件的管脚数,另一方面便于实现突发数据传输。在做数据传输时,由一个PCI设备做发起者(主控,Initiator或Master),而另一个PCI设备做目标(从设备,Target或Slave)。总线上的所有时序的产生与控制,都由Master来发起。PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定在谁有权力拿到总线的主控权。

当PCI总线进行操作时,发起者(Master)先置REQ#,当得到仲裁器(Arbiter)的许可时(GNT#),会将FRAME#置低,并在AD总线上放置Slave地址,同时C/BE#放置命令信号,说明接下来的传输类型。所有PCI总线上设备都需对此地址译码,被选中的设备要置DEVSEL#以声明自己被选中。然后当IRDY#与TRDY#都置低时,可以传输数据。当Master数据传输结束前,将FRAME#置高以标明只剩最后一组数据要传输,并在传完数据后放开IRDY#以释放总线控制权。

这里我们可以看出,PCI总线的传输是很高效的,发出一组地址后,理想状态下可以连续发数据,峰值速率为132MB/s。实际上,目前流行的33M@32bit北桥芯片一般可以做到100MB/s的连续传输。

(1)传输速率高最大数据传输率为132MB/s,当数据宽度升级到64位,数据传输率可达264MB/s。这是其他总线难以比拟的。它大大缓解了数据I/O瓶颈,使高性能CPU的功能得以充分发挥,适应高速设备数据传输的需要。

(2)多总线共存采用PCI总线可在一个系统中让多种总线共存,容纳不同速度的设备一起工作。通过HOST-PCI桥接组件芯片,使CPU总线和PCI总线桥接;通过PCI-ISA/EISA桥接组件芯片,将PCI总线与ISA/EISA总线桥接,构成一个分层次的多总线系统。高速设备从ISA/EISA总线卸下来,移到PCI总线上,低速设备仍可挂在ISA/EISA总线上,继承原有资源,扩大了系统的兼容性。

(3)独立于CPU PCI总线不依附于某一具体处理器,即PCI总线支持多种处理器及将来发展的新处理器,在更改处理器品种时,更换相应的桥接组件即可。

(4)自动识别与配置外设 用户使用方便。

(5)并行操作能力。

PCI总线的主要性能

(1)总线时钟频率33.3MHz/66.6MHz。

(2)总线宽度32位/64位。

(3)最大数据传输率132MB/s(264MB/s)。

(4)支持64位寻址。

(5)适应5V和3.3V电源环境。

所谓即插即用,是指当板卡插入系统时,系统会自动对板卡所需资源进行分配,如基地址、中断号等,并自动寻找相应的驱动程序。而不象旧的ISA板卡,需要进行复杂的手动配置。

实际的实现远比说起来要复杂。在PCI板卡中,有一组寄存器,叫"配置空间"(Configuration Space),用来存放基地址与内存地址,以及中断等信息。

以内存地址为例。当上电时,板卡从ROM里读取固定的值放到寄存器中,对应内存的地方放置的是需要分配的内存字节数等信息。操作系统要跟据这个信息分配内存,并在分配成功后把相应的寄存器中填入内存的起始地址。这样就不必手工设置开关来分配内存或基地址了。对于中断的分配也与此类似。

ISA卡的一个重要局限在于中断是独占的,而我们知道计算机的中断号只有16个,系统又用掉了一些,这样当有多块ISA卡要用中断时就会有问题了。

PCI总线的中断共享由硬件与软件两部分组成。

硬件上,采用电平触发的办法:中断信号在系统一侧用电阻接高,而要产生中断的板卡上利用三极管的集电极将信号拉低。这样不管有几块板产生中断,中断信号都是低;而只有当所有板卡的中断都得到处理后,中断信号才会恢复高电平。

软件上,采用中断链的方法:假设系统启动时,发现板卡A用了中断7,就会将中断7对应的内存区指向A卡对应的中断服务程序入口ISR_A;然后系统发现板卡B也用中断7,这时就会将中断7对应的内存区指向ISR_B,同时将ISR_B的结束指向ISR_A。以此类推,就会形成一个中断链。而当有中断发生时,系统跳转到中断7对应的内存,也就是ISR_B。ISR_B就要检查是不是B卡的中断,如果是,要处理,并将板卡上的拉低电路放开;如果不是,则呼叫ISR_A。这样就完成了中断的共享。

通过以上讨论,我们不难看出,PCI总线有着极大的的优势。而近年来的市场情况也证实了这一点。