时序逻辑电路是数字逻辑电路的重要组成部分,时序逻辑电路又称时序电路,主要由存储电路和组合逻辑电路两部分组成。它和我们熟悉的其他电路不同,其在任何一个时刻的输出状态由当时的输入信号和电路原来的状态共同决定,而它的状态主要是由存储电路来记忆和表示的。同时时序逻辑电路在结构以及功能上的特殊性,相较其他种类的数字逻辑电路而言,往往具有难度大、电路复杂并且应用范围广的特点。

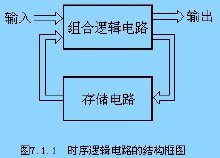

在数字电路通常分为组合逻辑电路和时序逻辑电路两大类,组合逻辑电路的有关内容在前面的章节里已经作了介绍,组合逻辑电路的特点是输入的变化直接反映了输出的变化,其输出的状态仅取决于输入的当前的状态,与输入、输出的原始状态无关,而时序电路是一种输出不仅与当前的输入有关,而且与其输出状态的原始状态有关,其相当于在组合逻辑的输入端加上了一个反馈输入,在其电路中有一个存储电路,其可以将输出的状态保持住,我们可以用下图的框图来描述时序电路的构成。

从上面的图上可以看出,其输出是输入及输出前一个时刻的状态的函数,这时就无法用组合逻辑电路的函数表达式的方法来表示其输出函数表达式了,在这里引入了现态(Present state)和次态(Next State)的概念,当现态表示现在的状态(通常用Qn来表示),而次态表示输入发生变化后其输出的状态 (通常用Qn 1表示),那么输入变化后的输出状态表示为

Qn 1=f(X,Qn)

其中:X为输入变量。

下面通过两个波形图来帮助建立时序电路中存储器的概念:

从上图a图中可以看出,其图中有四段输入RS都为0的情况,但其输出Q的状态不同,这取决于输出的原始状态;而b图中的输入与图a相同,但多了一个CP,这时输出Q不仅取决于输入RS、输出Q的原始状态,而且取决CP的状态,仅当CP为高电平时,输入的状态才能影响输出的状态。通常将上面的两种类型分为两种形式的存储器电路:锁存器(Latch)和触发器(Flip-flop),其两者的区别在于其输出状态的变化是否取决于CP(时钟脉冲Clock Pulse)。将图a所有的电路称为锁存器,而b图所示的电路称为触发器电路。

时序逻辑电路的特点:任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关,所以时序电路具有记忆功能。