第1章 高速系统设计简介

1.1 PCB设计技术回顾

1.2 什么是“高速”系统设计

1.3 如何应对高速系统设计

1.3.1 理论作为指导和基准

1.3.2 实践经验积累

1.3.3 时间效率平衡

1.4 小结

第2章 高速系统设计理论基础

2.1 微波电磁波简介

2.2 微波传输线

2.2.1 微波等效电路物理量

2.2.2 微波传输线等效电路

2.3 电磁波反射

2.4 微波传输介质

2.4.1 微带线Microstrip Line

2.4.2 微带线的损耗

2.4.3 带状线Strip Line

2.4.4 同轴线Coaxial Line

2.4.5 双绞线 Twist Line

2.4.6 差分传输线

2.4.7 差分阻抗

2.5 “阻抗”的困惑

2.5.1 阻抗的定义

2.5.2 为什么要考虑阻抗

2.5.3 传输线结构和传输线阻抗

2.5.4 瞬时阻抗和特征阻抗

2.5.5 特征阻抗和信号完整性

2.5.6 为什么是50Ω

2.6 阻抗的测量

2.7 “阻抗”的困惑之答案

2.8 小结

第3章 信号完整性简介

3.1 什么是信号完整性

3.2 信号完整性问题分类

3.3 反射的产生和预防

3.3.1 反射的产生

3.3.2 反射的消除和预防

3.3.2.1 匹配

3.3.2.2 拓扑结构设计

3.4 串扰的产生和预防

3.4.1 串扰的产生

3.4.2 串扰的预防与消除

3.5 电源完整性分析

3.5.1 电源系统设计目标

3.5.2 电源系统设计方法

3.5.3 电容的理解

3.5.4 SSN分析和应用

3.6 电磁兼容性EMC和电磁干扰EMI

3.7 影响信号完整性的其他因素

3.8 小结

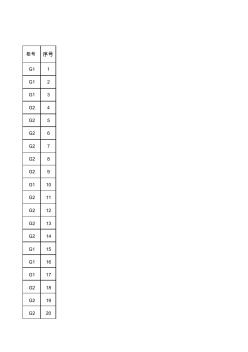

第4章 Cadence高速系统设计工具

4.1 Cadence高速系统设计流程

4.2 约束管理器Constrain Manager

4.3 SigXplorer信号完整性分析工具

4.3.1 S参数(Scattering parameters)

4.3.2 过孔模型生成(Via Modeling)

4.3.3 通道分析CA(Channel Analysis)

4.4 前仿和后仿

第5章 Cadence高速系统设计流程及工具使用

5.1 高速电路设计流程的实施条件分析

5.2 IBIS模型和DML模型

5.2.1 IBIS模型介绍

5.2.2 IBIS文件介绍

5.2.3 DML模型

5.2.4 如何获得IBIS模型

5.2.5 在Cadence中使用IBIS模型

5.2.6 IBIS2 SigNoise的警告和错误参考

5.3 仿真库的建立和设置

5.4 仿真分析条件设置

5.4.1 Cross-section——PCB叠层设置

5.4.2 DC Nets——直流电压设置

5.4.3 Devices——器件类型和管脚属性设置

5.4.4 SI Models——为器件指定模型

5.4.5 SI Audit——仿真条件的检查

5.5 系统设计和(预)布局

5.6 使用SigXP进行仿真分析

5.6.1 拓扑结构抽取

5.6.2 在SigXP中进行仿真

5.6.2.1 设置激励和仿真类型

5.6.2.2 设置仿真参数

5.6.2.3 查看仿真结果

5.6.2.4 为什么要进行参数扫描仿真

5.7 约束规则生成

5.7.1 简单约束设计——Prop Delay

5.7.2 拓扑约束设计——Wiring

5.7.3 时序相关约束设计——Switch-Settle Delay

5.8 约束规则的应用

5.8.1 层次化约束关系

5.8.2 约束规则的映射

5.8.3 Constrain Mananer的使用

5.9 布线后的仿真分析和验证

5.9.1 布线后仿真的必要性

5.9.2 布线后仿真流程

5.10 电源完整性设计

5.10.1 电源完整性设计方法

5.10.2 电源完整性设计分析步骤

5.10.3 多节点仿真分析

5.10.4 电容的布局和布线

5.10.5 合理认识电容的有效去耦半径

5.11 SSN的设计分析

5.12 小结

第6章 高速系统设计实例设计分析

6.1 设计实例介绍

6.2 DDR设计分析

6.2.1 DDR规范的DC和AC特性

6.2.2 DDR规范的时序要求

6.2.3 DDR芯片的电气特性和时序要求

6.2.4 DDR控制器的电气特性和时序要求

6.3 仿真库的建立

6.3.1 DDR芯片的IBIS文件处理

6.3.2 FPGA的IBIS模型文件处理

6.3.3 仿真库的建立

6.4 仿真条件设置——Setup Advisor

6.4.1 设置叠层和阻抗特性

6.4.2 设置电压

6.4.3 器件类型和模型设置

6.5 (预)布局

6.6 仿真约束的生成和实施

6.6.1 网络整理和仿真对象规划

6.6.2 结构抽取与仿真分析

6.6.3 DDR地址总线约束定义

6.6.4 DDR数据总线仿真分析和约束

6.6.4.1 DDR数据总线仿真分析

6.6.4.2 DDR数据总线时序仿真分析

6.6.5 DDR数据总线约束定义

6.6.6 约束的时序验证

6.7 约束实施和布线

6.8 布线后的仿真验证0

6.9 DDR总线的其他分析技术

6.9.1 DDR2和DDR3介绍

6.9.2 DDR2仿真分析设计方法

6.9.3 DIMM系统设计分析方法

6.10 电源完整性——多节点仿真分析

6.11 灵活使用Cadence高速设计流程

第7章 高速串行差分信号仿真分析及技术发展挑战

7.1 高速串行信号介绍

7.2 Cadence中高速串行信号仿真分析流程和方法

7.2.1 系统级设计

7.2.2 互连设计和S参数

7.2.3 通道分析和预加重设计

7.2.4 时域分析和验证

7.3 3.125Gbps差分串行信号设计实例仿真分析

7.3.1 设计用例说明

7.3.2 设计用例解析

7.3.3 设计用例的使用

7.4 高速串行信号设计挑战

7.4.1 有损传输线和PCB材料的选择

7.4.2 高频差分信号的布线和匹配设计

7.4.3 过孔的Stub效应

7.4.4 连接器信号分布

7.4.5 预加重和均衡

7.4.6 阻抗,还是阻抗

7.4.7 6 Gbps,12 Gbps!然后

7.5 5Gbps以上的高速差分串行信号仿真和IBIS-AMI模型

7.5.1 5 Gbps以上的高速差分串行信号仿真

7.5.2 IBIS-AMI模型

7.6 抖动(Jitter)

7.6.1 认识抖动(Jitter)

7.6.2 实时抖动分析

7.6.3 抖动各分量的典型特征

第8章 实战后的思考

参考书目

术语和缩略词2100433B

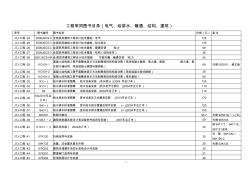

电厂图书目录

电厂图书目录

工程常用图书目录

工程常用图书目录