过去数十年来,金氧半场效晶体管的尺寸不断地变小。早期的集成电路金氧半场效晶体管工艺里,沟道长度约在几个微米的档次。但是到了今日的集成电路工艺,这个参数已经缩小了几十倍甚至超过一百倍。2008年初,Intel开始以45奈米的技术来制造新一代的微处理器,实际的组件沟道长度可能比这个数字还小一些。至90年代末,金氧半场效晶体管尺寸不断缩小,让集成电路的性能大大提升,而从历史的角度来看,这些技术上的突破和半导体工艺的进步有着密不可分的关系。

金属氧化物半导体场效应晶体管尺寸缩小

MOSFET在概念上属于“绝缘栅极场效应晶体管”(insulated-Gate Field Effect Transistor, IGFET)。而IGFET的栅极绝缘层,有可能是其他物质,而非MOSFET使用的氧化层。有些人在提到拥有多晶硅栅极的场效应晶体管组件时比较喜欢用IGFET,但是这些IGFET多半指的是MOSFET。

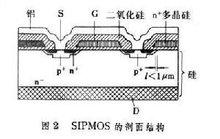

MOSFET里的氧化层位于其通道上方,依照其操作电压的不同,这层氧化物的厚度仅有数十至数百埃(Å)不等,通常材料是二氧化硅(silicon dioxide, SiO2),不过有些新的高级制程已经可以使用如氮氧化硅(silicon oxynitride, SiON)做为氧化层之用。

今日半导体组件的材料通常以硅(silicon)为首选,但是也有些半导体公司发展出使用其他半导体材料的制程,当中最著名的例如IBM使用硅与锗(germanium)的混合物所发展的硅锗制程(silicon-germanium process, SiGe process)。而可惜的是很多拥有良好电性的半导体材料,如砷化镓(galliumarsenide, GaAs),因为无法在表面长出品质够好的氧化层,所以无法用来制造MOSFET组件。

当一个够大的电位差施于MOSFET的栅极与源极(source)之间时,电场会在氧化层下方的半导体表面形成感应电荷,而这时所谓的“反转通道”(inversion channel)就会形成。通道的极性与其漏极(drain)与源极相同,假设漏极和源极是n-type,那么通道也会是n-type。通道形成后,MOSFET即可让电流通过,而依据施于栅极的电压值不同,可由MOSFET的通道流过的电流大小亦会受其控制而改变。

金属氧化物半导体场效应晶体管负面效应

虽然金氧半场效晶体管尺寸缩小可以带来很多好处,但同时也有很多负面效应伴随而来。

把金氧半场效晶体管的尺寸缩小到一微米以下对于半导体工艺而言是个挑战,不过新挑战多半来自尺寸越来越小的金氧半场效晶体管组件所带来过去不曾出现的物理效应。

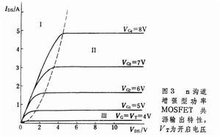

由于金氧半场效晶体管栅极氧化层的厚度也不断减少,所以栅极电压的上限也随之变少,以免过大的电压造成栅极氧化层雪崩击穿(breakdown)。为了维持同样的性能,金氧半场效晶体管的临界电压也必须降低,但是这也造成了金氧半场效晶体管越来越难以完全关闭。也就是说,足以造成金氧半场效晶体管沟道区发生弱反转的栅极电压会比从前更低,于是所谓的亚阈值电流(subthreshold current)造成的问题会比过去更严重,特别是今日的集成电路芯片所含有的晶体管数量剧增,在某些超大规模集成电路的芯片,次临限传导造成的功率消耗竟然占了总功率消耗的一半以上。

不过反过来说,也有些电路设计会因为金氧半场效晶体管的次临限传导得到好处,例如需要较高的转导/电流转换比(transconductance-to-current ratio)的电路里,利用次临限传导的金氧半场效晶体管来达成目的的设计也颇为常见。

传统上,互补式金属氧化物半导体逻辑门的切换速度与其组件的栅极电容有关。但是当栅极电容随着金氧半场效晶体管尺寸变小而减少,同样大小的芯片上可容纳更多晶体管时,连接这些晶体管的金属导线间产生的寄生电容效应就开始主宰逻辑门的切换速度。如何减少这些寄生电容,成了芯片效率能否向上突破的关键之一。

当芯片上的晶体管数量大幅增加后,有一个无法避免的问题也跟着发生了,那就是芯片的发热量也大幅增加。一般的集成电路组件在高温下工作可能会导致切换速度受到影响,或是导致可靠度与寿命的问题。在一些发热量非常高的集成电路芯片如微处理器,需要使用外加的散热系统来缓和这个问题。

在功率晶体管(Power金氧半场效晶体管)的领域里,沟道电阻常常会因为温度升高而跟着增加,这样也使得在组件中PN结(pn-junction)导致的功率损耗增加。假设外置的散热系统无法让功率晶体管的温度保持在够低的水准,很有可能让这些功率晶体管遭到热失控的命运。

栅极氧化层随着金氧半场效晶体管尺寸变小而越来越薄,主流的半导体工艺中,甚至已经做出厚度仅有1.2奈米的栅极氧化层,大约等于5个原子叠在一起的厚度而已。在这种尺度下,所有的物理现象都在量子力学所规范的世界内,例如电子的穿隧效应。因为穿隧效应,有些电子有机会越过氧化层所形成的位能障壁(potential barrier)而产生漏电流,这也是今日集成电路芯片功耗的来源之一。

为了解决这个问题,有一些介电系数比二氧化硅更高的物质被用在栅极氧化层中。例如铪和锆的金属氧化物(二氧化铪、二氧化锆)等高介电系数的物质均能有效降低栅极漏电流。栅极氧化层的介电系数增加后,栅极的厚度便能增加而维持一样的电容大小。而较厚的栅极氧化层又可以降低电子通过穿隧效应穿过氧化层的机率,进而降低漏电流。不过利用新材料制作的栅极氧化层也必须考虑其位能障壁的高度,因为这些新材料的传导带和价带和半导体的传导带与价带的差距比二氧化硅小(二氧化硅的传导带和硅之间的高度差约为8ev),所以仍然有可能导致栅极漏电流出现。

现代的半导体工艺工序复杂而繁多,任何一道工艺都有可能造成集成电路芯片上的组件产生些微变异。当金氧半场效晶体管等组件越做越小,这些变异所占的比例就可能大幅提升,进而影响电路设计者所预期的性能,这样的变异让电路设计者的工作变得更为困难。

单Halo全耗尽应变Si绝缘硅金属氧化物半导体场效应管的阈值电压解析模型

单Halo全耗尽应变Si绝缘硅金属氧化物半导体场效应管的阈值电压解析模型

围栅金属氧化物半导体场效应管电流模型

围栅金属氧化物半导体场效应管电流模型