一般的晶体管是由两种极性的载流子,即多数载流子和反极性的少数载流子参与导电,因此称为双极型晶体管,而FET仅是由多数载流子参与导电,它与双极型相反,也称为单极型晶体管。它属于电压控制型半导体器件,具有输入电阻高(10^8~10^9Ω)、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点,现已成为双极型晶体管和功率晶体管的强大竞争者

在两个高掺杂的P区中间,夹着一层低掺杂的N区(N区一般做得很薄),形成了两个PN结。在N区的两端各做一个欧姆接触电极,在两个P区上也做上欧姆电极,并把这两P区连起来,就构成了一个场效应管。

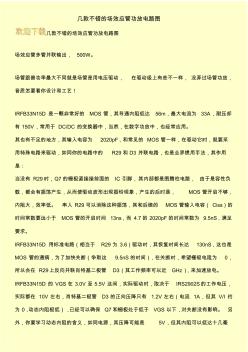

N型导电沟道结型场效应管的电路符号。

将两个P区的引出线连在一起作为一个电极,称为栅极,在N型硅片两端各引出一个电极,分别称为源极和漏极,很薄的N区称为导电沟道。共漏极放大电路--源极输出器

栅极简称为G ,源极简称为S,漏极简称为D。

-