设计收敛集成电路设计文献

厦门集成电路设计流片补贴项目

厦门集成电路设计流片补贴项目

厦门集成电路设计流片补贴项目

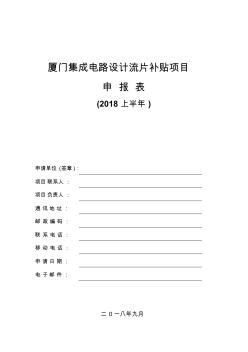

厦门集成电路设计流片补贴项目 申 报 表 (2018 上半年 ) 申请单位 (签章 ): 项目联系人 : 项目负责人 : 通 讯地 址: 邮 政 编 码 : 联 系 电 话 : 移 动 电 话 : 申 请日 期: 电 子邮 件: 二 0一八年九月 目录 1、厦门集成电路设计流片补贴资金申请表 (包括 MPW、工 程批 ) 2、申请补贴资金明细表 3、企业基本情况 4、产品研发说明 5、芯片版图缩略图 (需用彩印 ) 6、流片加工发票复印件 7、流片合同复印件 8、付款凭证(境外加工的需提供报关单或委外加工证明) 9、正版软件使用证明(需用原件) 10、2017年度财务审计报告、 6月份财务报表 (现金流量表、 损益表、资产负债表) (需用原件) 11、企业营业执照、税务登记证或三证合一复印件 12、产品外观照片等相关材料 厦门集成电路设计流片补贴资金申请表 类别 :MPW□ /工程批

测试服务指引-苏州中科集成电路设计中心苏州中科集成电路设计中心

测试服务指引-苏州中科集成电路设计中心苏州中科集成电路设计中心

测试服务指引-苏州中科集成电路设计中心苏州中科集成电路设计中心

测试服务指南 Suzhou CAS IC Design Center 苏州中科集成电路设计中心 Page 1 of 2 测试服务指南 ( IC 测试部) 1. 测试服务类型 1.1 测试技术服务 9 IC 验证测试:在硅芯片级和系统级上进行 IC 验证和调试,查找设计和工艺问题引 起的芯片错误 9 IC 特性测试: IC 特性分析,为 IC Datasheet 提供数据 9 IC 生产测试: IC 产品测试和筛选 9 IC 测试程序开发 9 DIB 设计和制作 9 测试技术支持 ? 测试向量转换 ? 测试技术咨询 ? DFT (可测试性设计)和 DFD(可调试性设计)设计咨询 9 测试技术培训 ? 测试方法、测试设备、测试开发、测量等基础技术培训 ? 测试机台技术培训 ? 测试程序开发技术培训 1.2 测试机时租赁 9 V93000 数字、模拟和混合信号集成电路测试系统 9